# **Table of Contents**

| Chapter 1 Bus Decode             | 1  |

|----------------------------------|----|

| Basic operation                  | 1  |

| Add a Bus Decode                 | 1  |

| Advance channel setting          | 2  |

| Specially Bus Decode             | 4  |

| Bus Decode Settings Introduction | 7  |

| 1-Wire                           | 8  |

| 10BASE-T1S                       | 11 |

| 3-Wire                           |    |

| 7-Segment                        | 15 |

| 8b10b Decoding                   | 17 |

| A/D Converter                    |    |

| Accelerometer                    | 22 |

| AD-Mux Flash                     | 24 |

| APML                             | 25 |

| AVSBus                           | 28 |

| BiSS-C                           | 30 |

| BSD                              | 33 |

| BSS                              | 34 |

| BT1120                           | 36 |

| CAN 2.0B/ CAN FD                 | 38 |

| CEC                              | 41 |

| Closed Caption                   | 43 |

| Codec SSI                        | 44 |

| DALI                             | 45 |

| DDC (EDID)                | 47  |

|---------------------------|-----|

| DMX512                    | 49  |

| DP Aux Ch                 | 50  |

| eSPI                      | 52  |

| FlexRay                   | 54  |

| HD Audio                  | 56  |

| HDLC                      | 58  |

| HDQ                       | 60  |

| HID Over I <sup>2</sup> C | 62  |

| HID Over SPI              | 64  |

| HTSensor                  | 65  |

| HyperBus                  | 67  |

| I <sup>2</sup> C          | 70  |

| I <sup>2</sup> C EEPROM   | 73  |

| I <sup>2</sup> S          | 75  |

| 180                       | 78  |

| IDE                       | 80  |

| IO-Link                   | 84  |

| IrDA                      | 87  |

| ISELED                    | 89  |

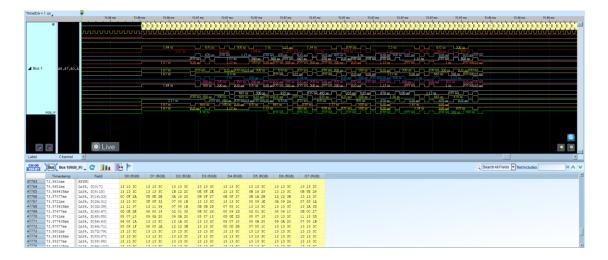

| ITU656 (CCIR656)          | 91  |

| JTAG                      | 93  |

| JVC IR                    | 98  |

| LCD1602                   | 99  |

| LED_Ctrl                  | 101 |

| LIN                       | 102 |

| Line Decoding                           | 105 |

|-----------------------------------------|-----|

| Line Encoding                           | 110 |

| LPC                                     | 117 |

| LPT                                     | 119 |

| LTPI                                    | 121 |

| Math                                    | 123 |

| M-Bus                                   | 127 |

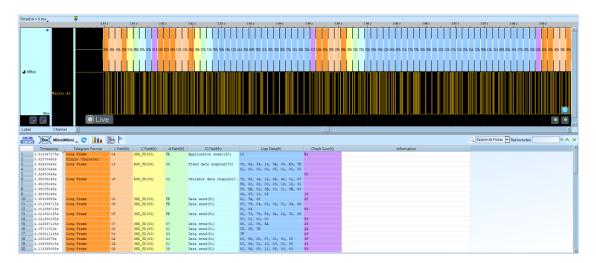

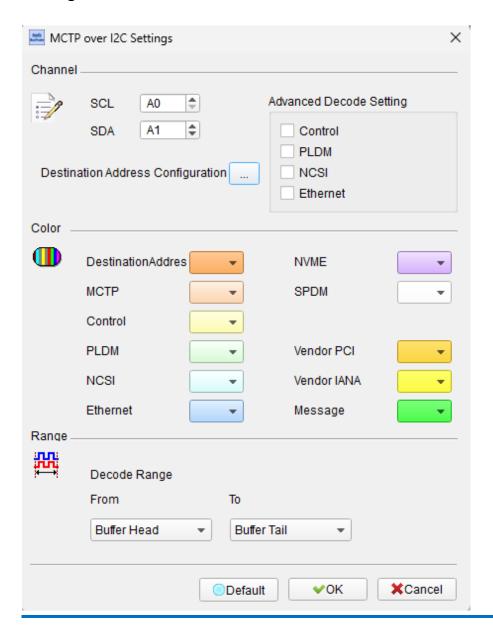

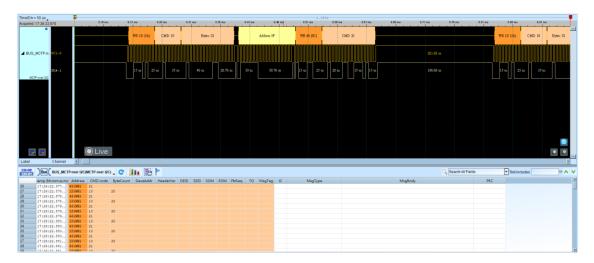

| MCTP over I <sup>2</sup> C              | 129 |

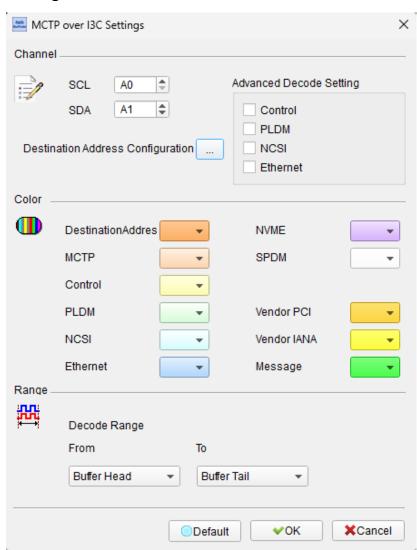

| MCTP over I3C                           | 131 |

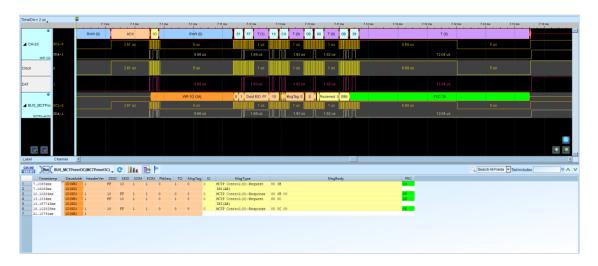

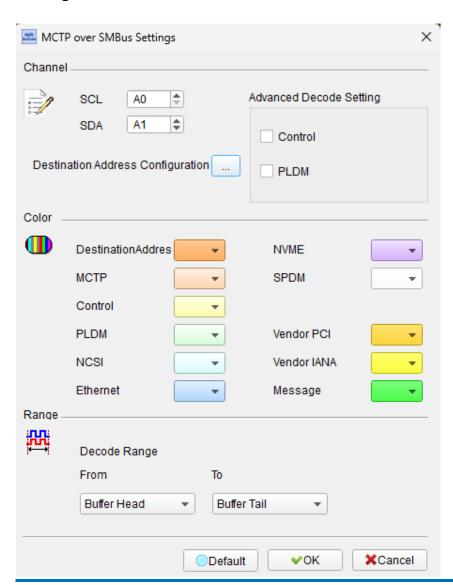

| MCTP over SMBus                         | 133 |

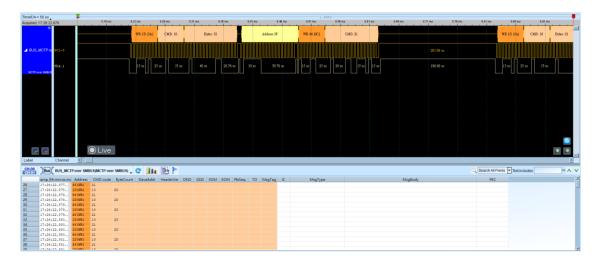

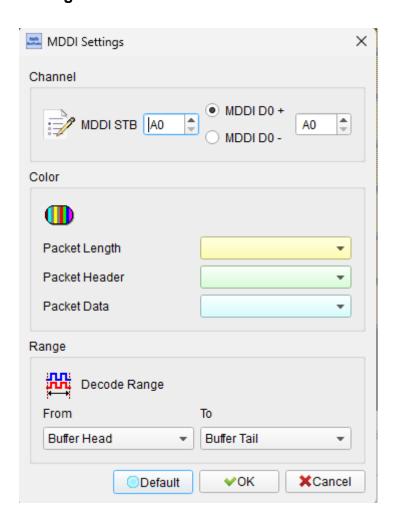

| Mobile Display Digital Interface (MDDI) | 135 |

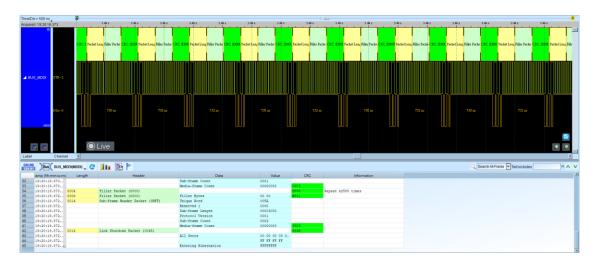

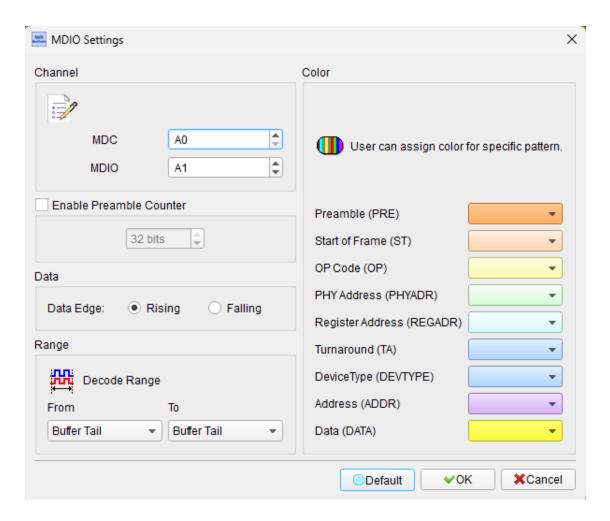

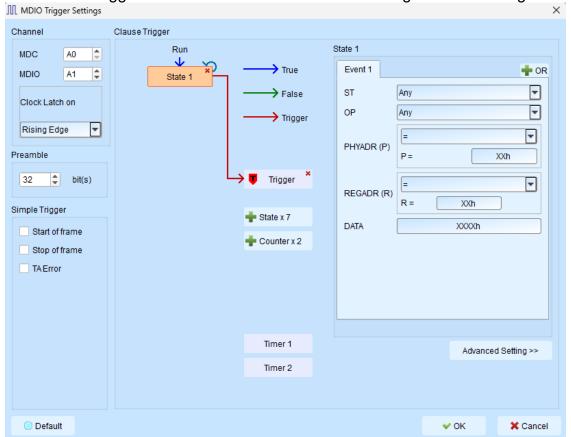

| MDIO                                    | 137 |

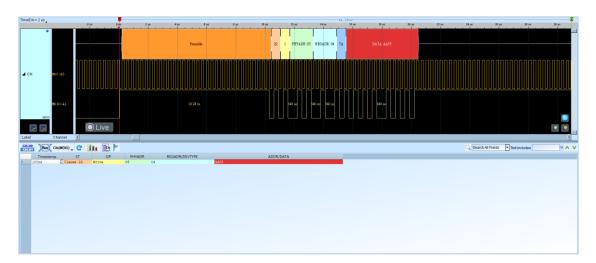

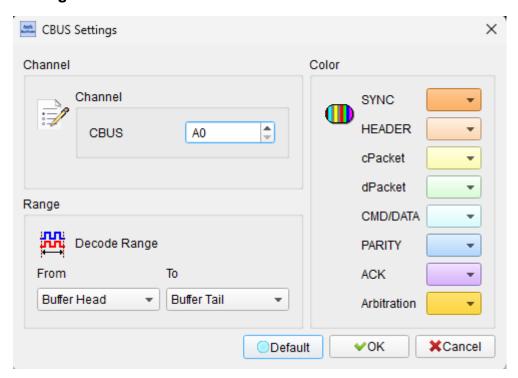

| MHL-CBUS                                | 139 |

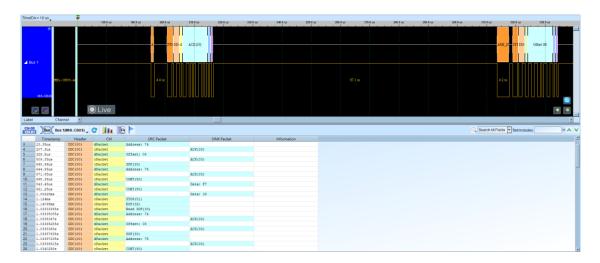

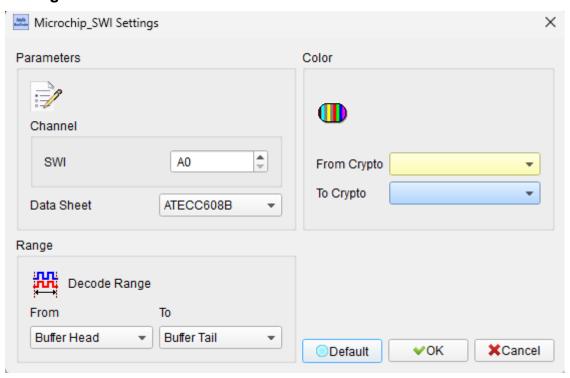

| Microchip SWI                           | 140 |

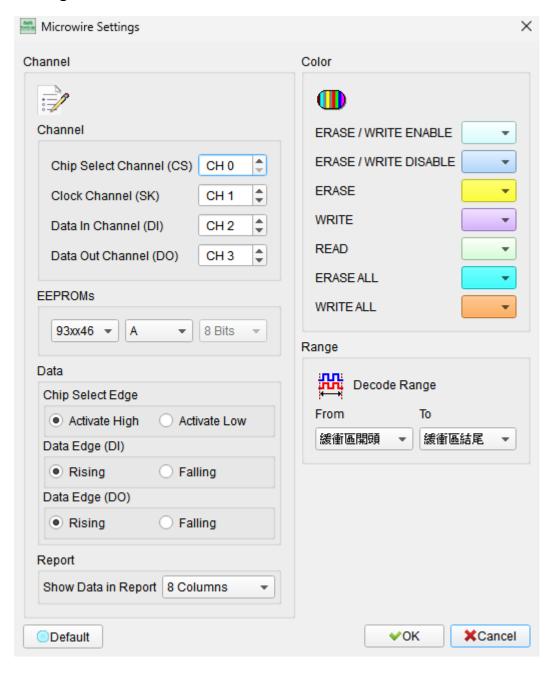

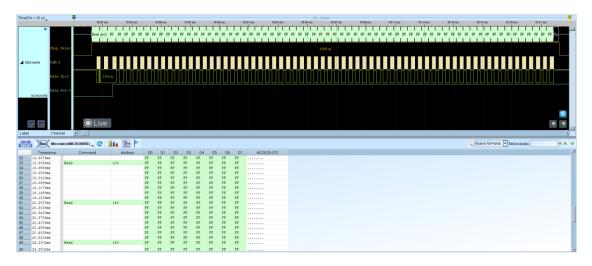

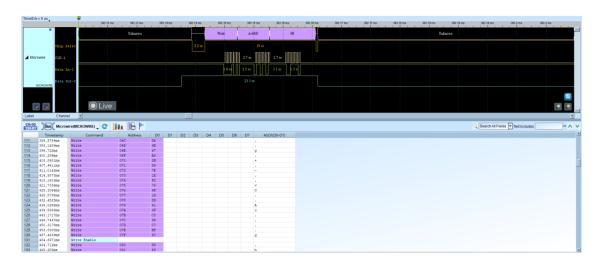

| Microwire                               | 141 |

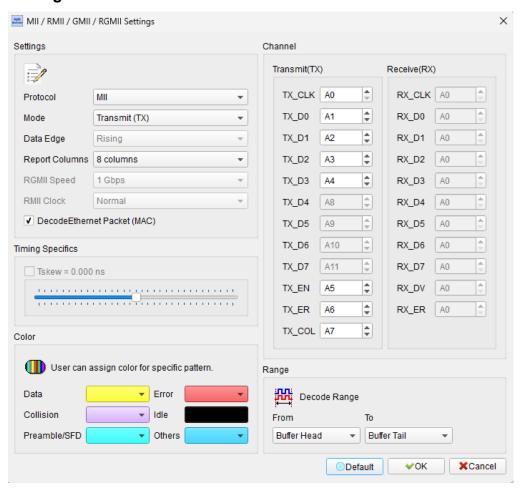

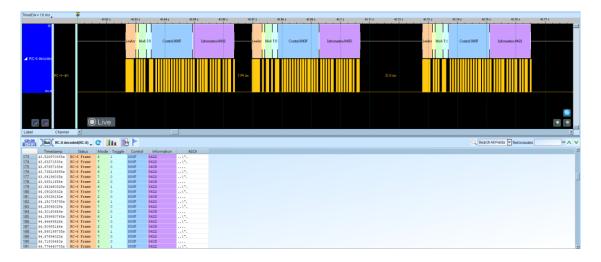

| MII / RMII / RGMII / GMII               | 143 |

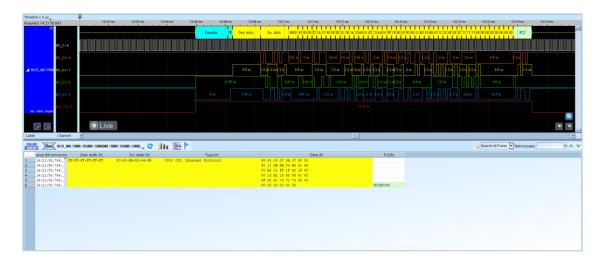

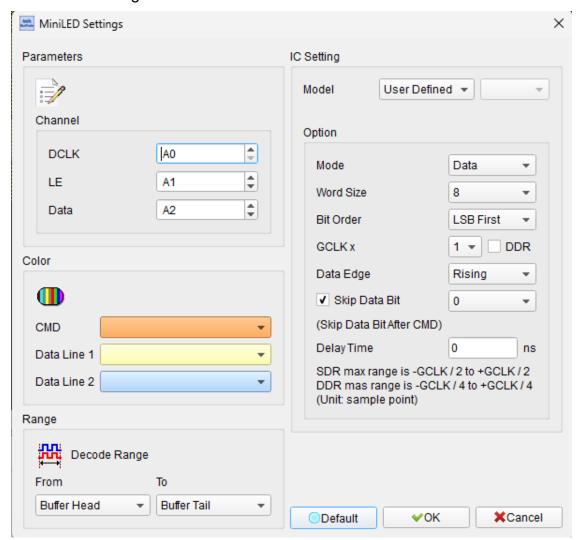

| Mini / Micro-LED                        | 146 |

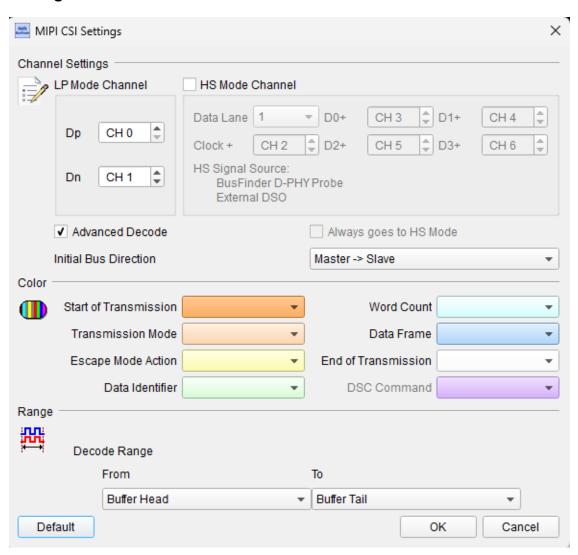

| MIPI CSI                                | 148 |

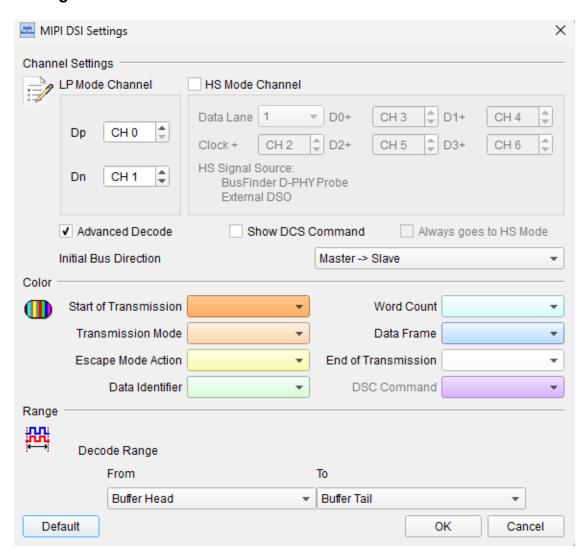

| MIPI DSI                                | 150 |

| MIPI I3C                                | 152 |

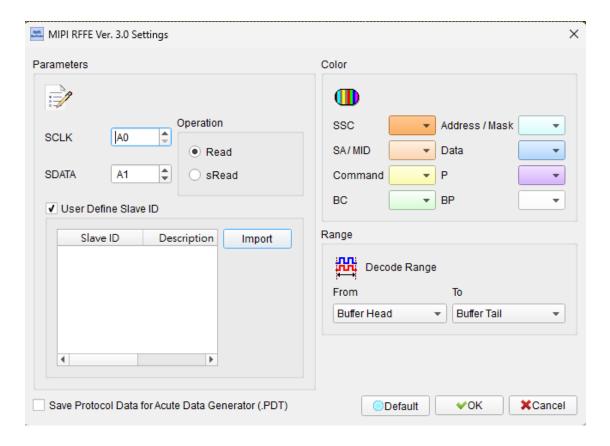

| MIPI RFFE                               | 155 |

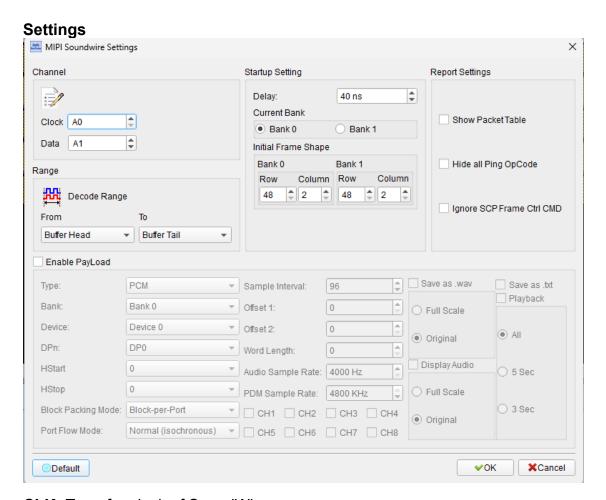

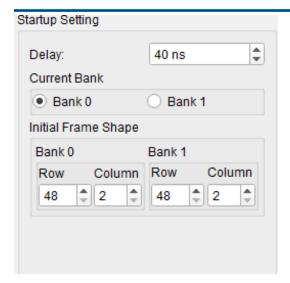

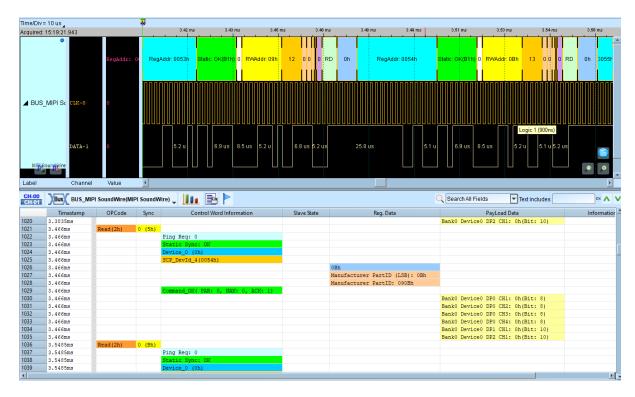

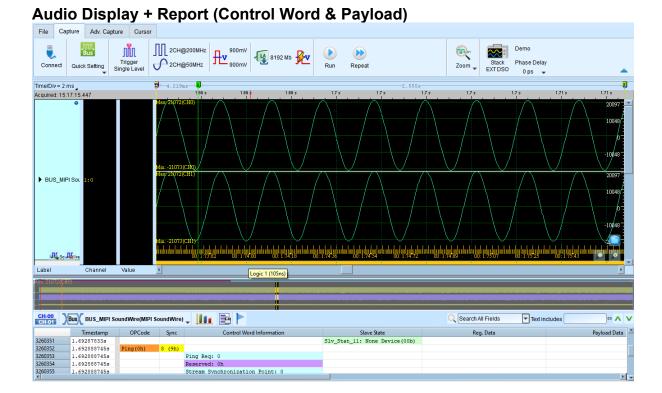

| MIPI SoundWire                          | 157 |

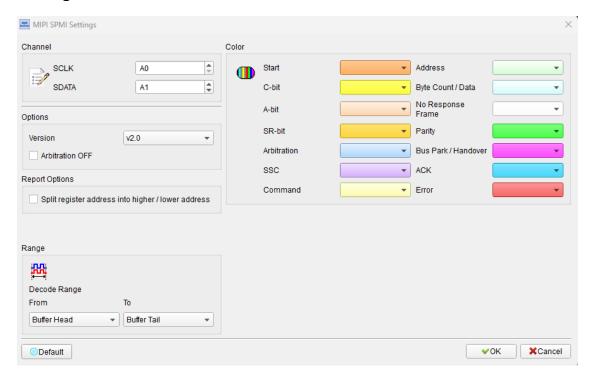

| MIPI SPMI                               | 162 |

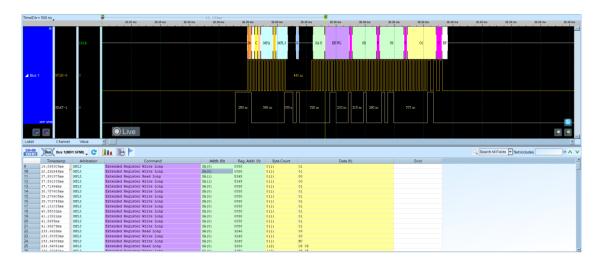

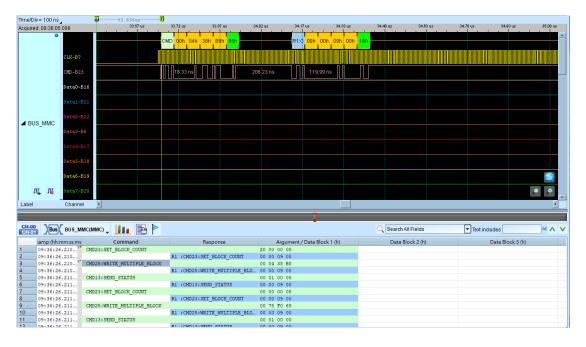

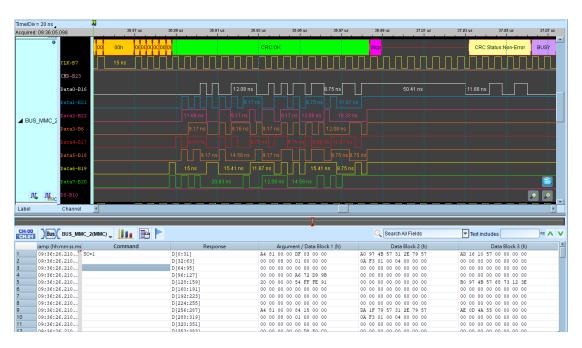

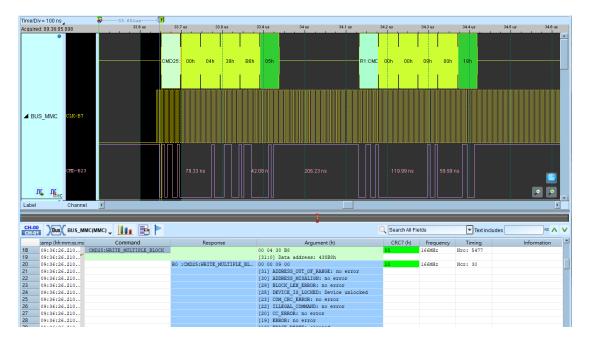

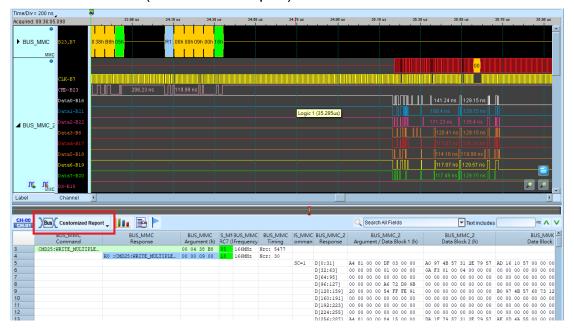

| MMC                                     | 164 |

| M-PESTI                                 | 168 |

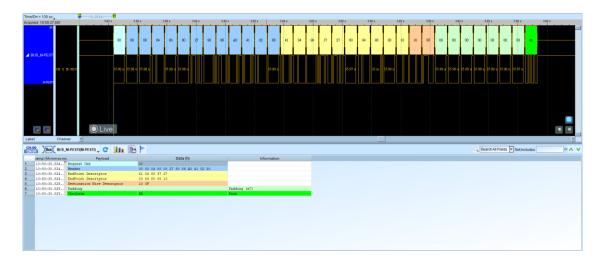

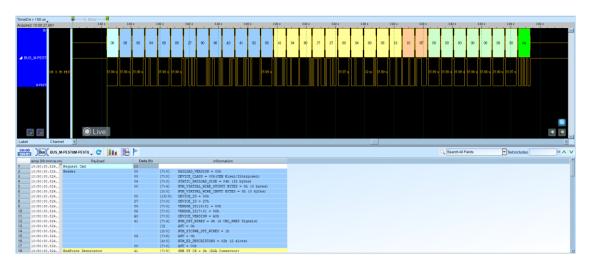

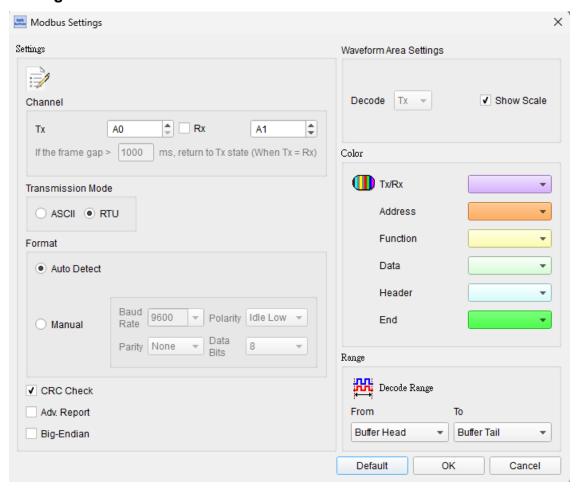

| ModBus                                  | 170 |

| NAND Flash     | 172 |

|----------------|-----|

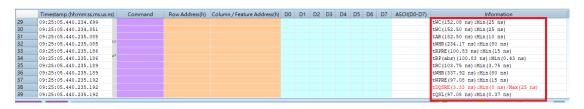

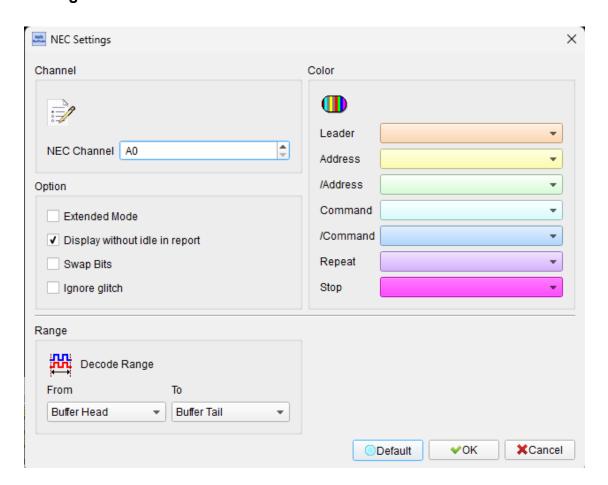

| NEC IR         | 185 |

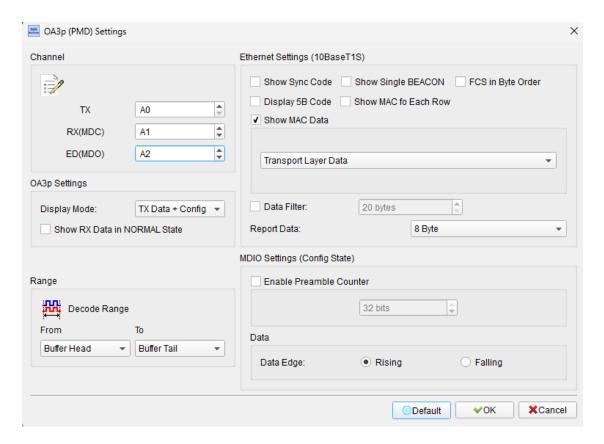

| OA3p(PMD)      | 187 |

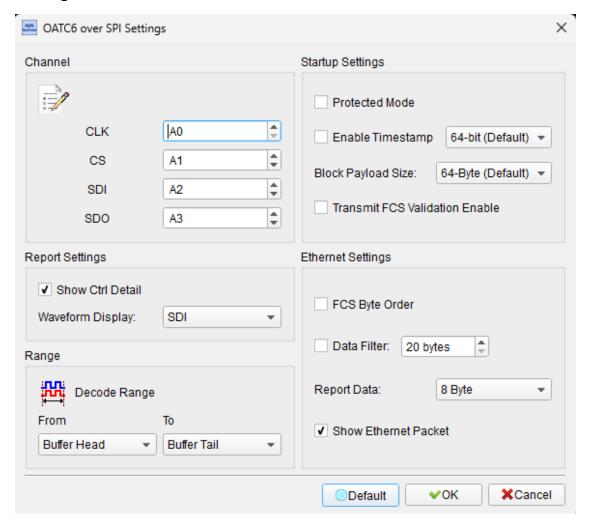

| OATC6 over SPI | 189 |

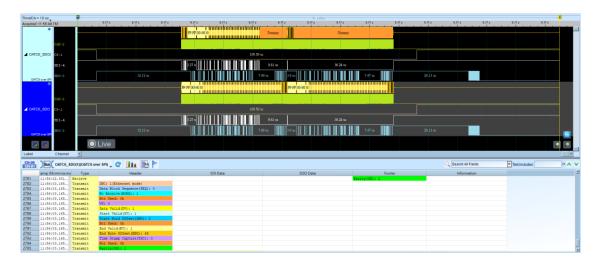

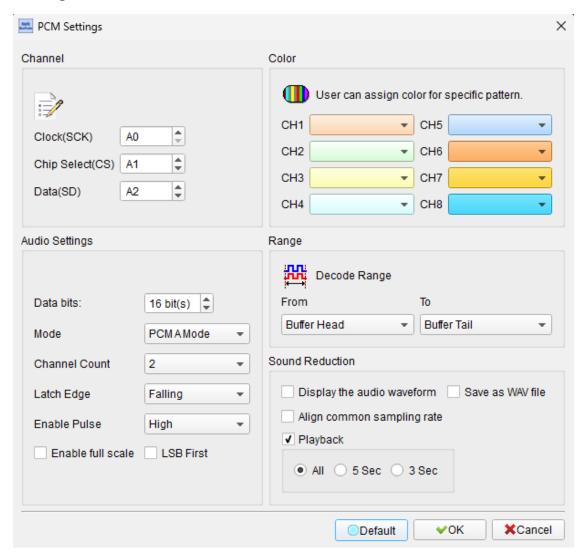

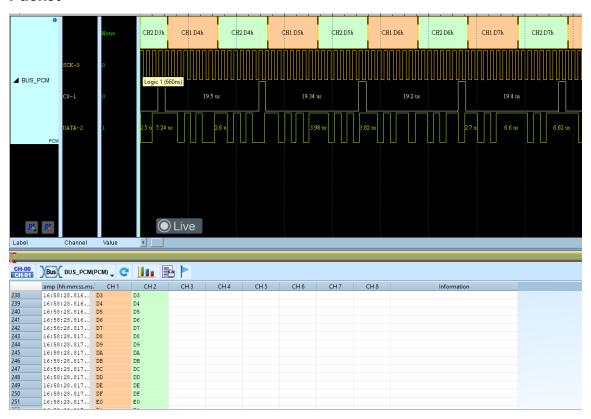

| PCM            | 192 |

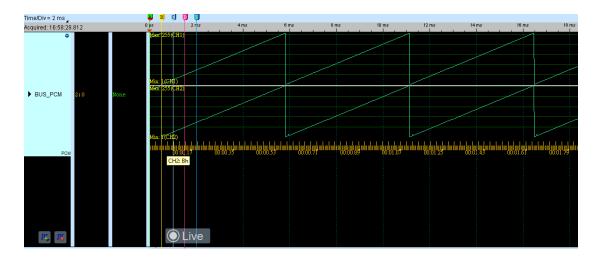

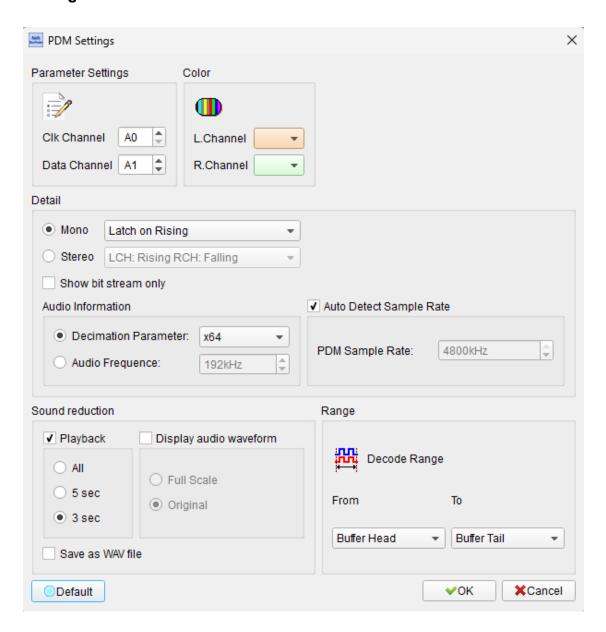

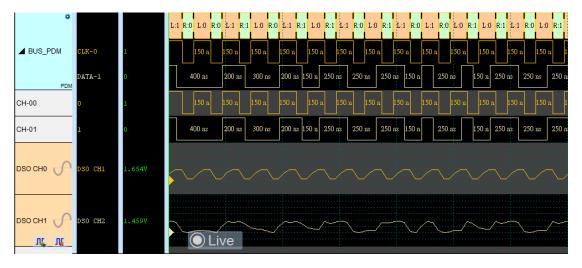

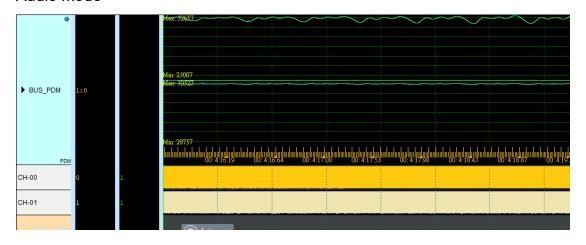

| PDM            | 195 |

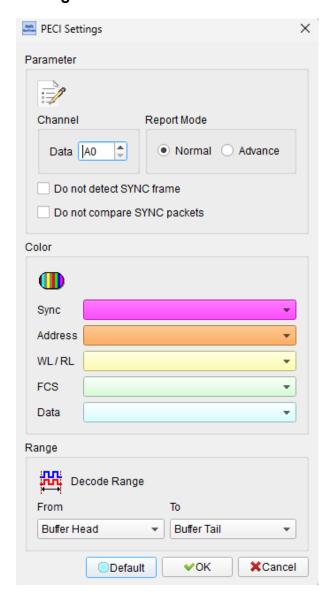

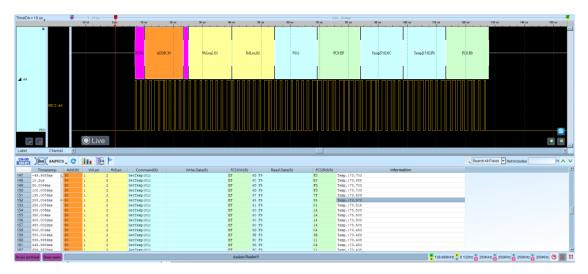

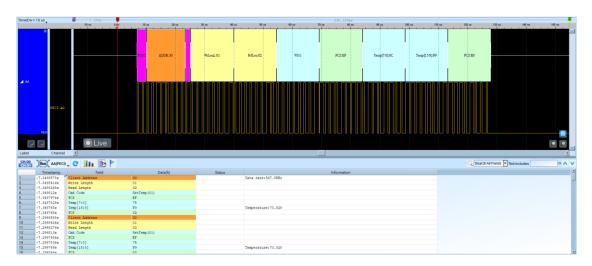

| PECI           | 197 |

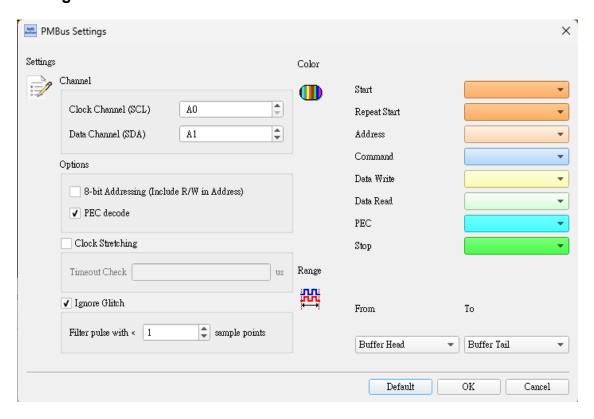

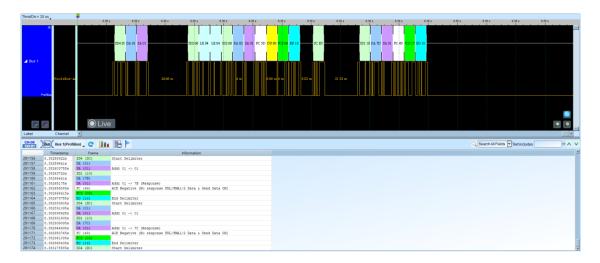

| PMBus          | 199 |

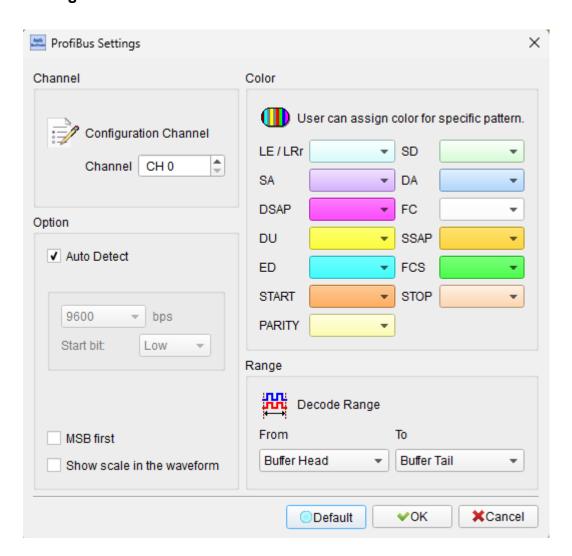

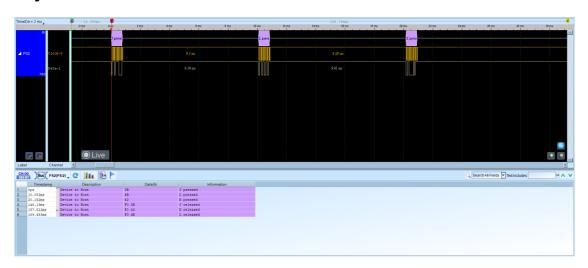

| ProfiBus       | 201 |

| PS/2           | 203 |

| PWM            | 206 |

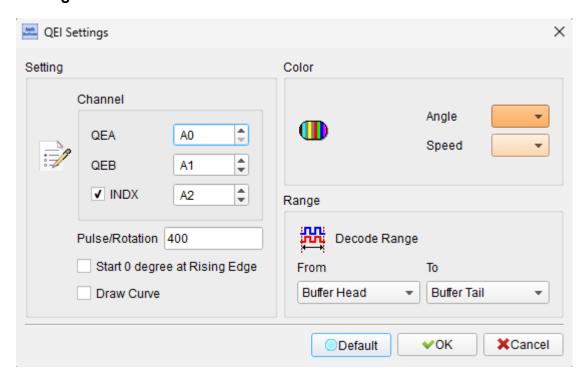

| QEI            | 211 |

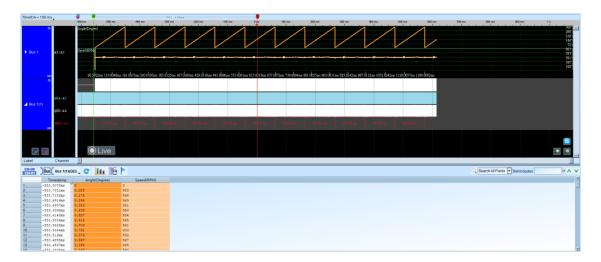

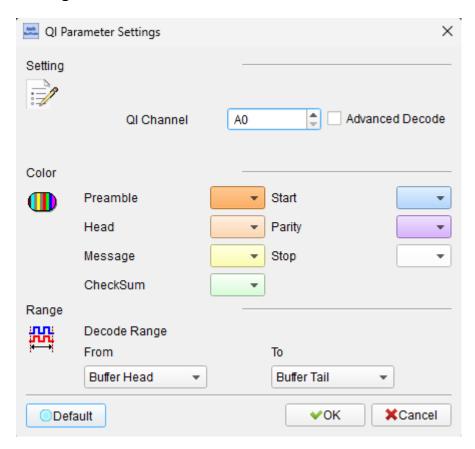

| QI             | 213 |

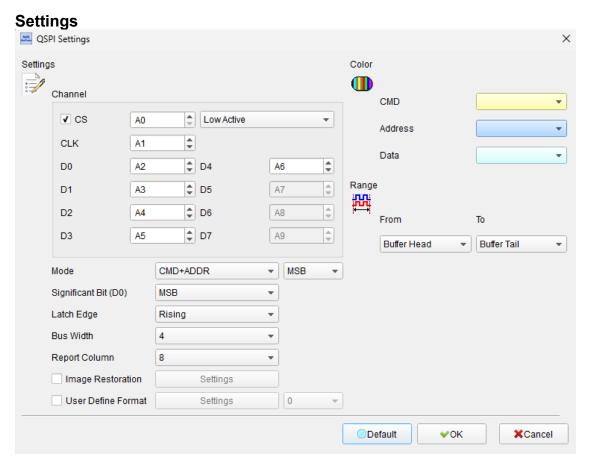

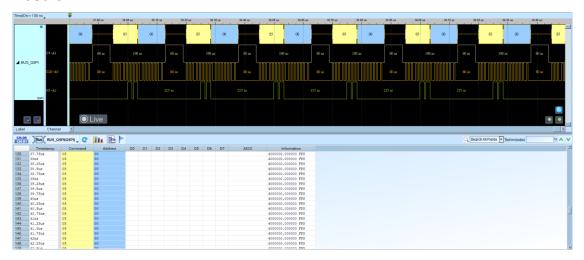

| QSPI           | 215 |

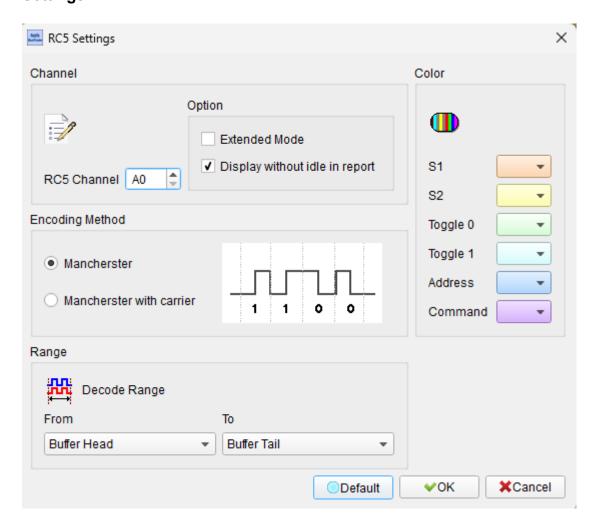

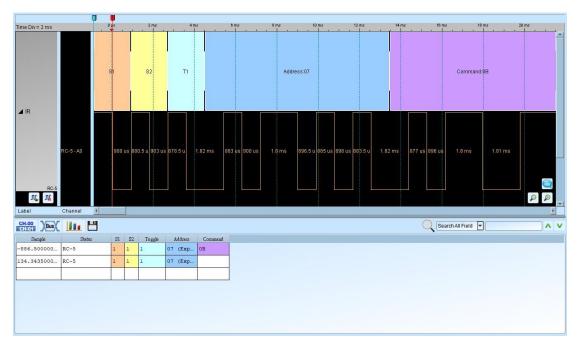

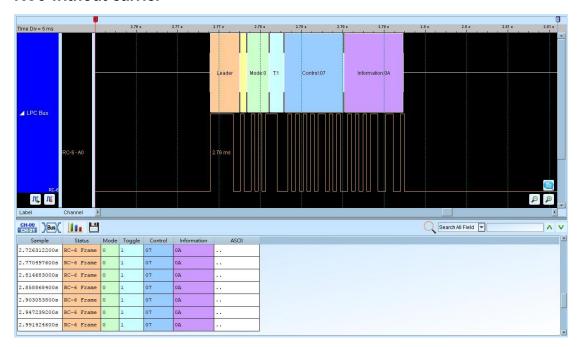

| RC-5           | 217 |

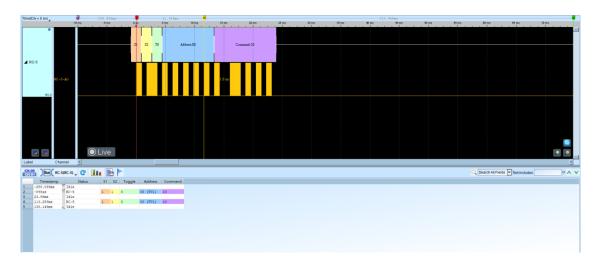

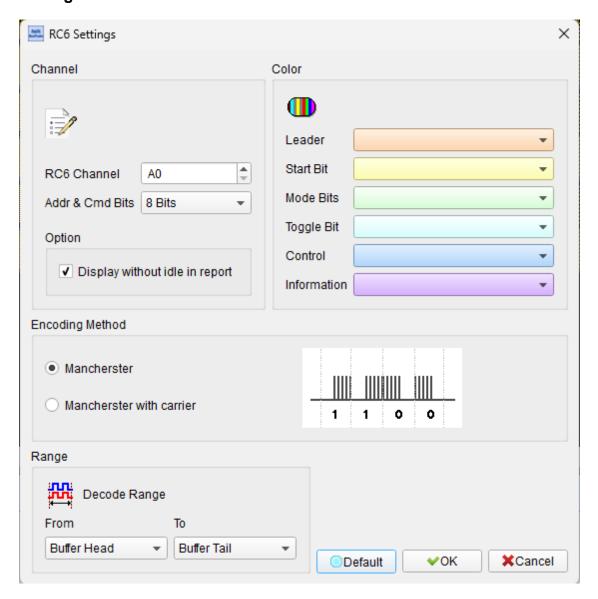

| RC-6           | 219 |

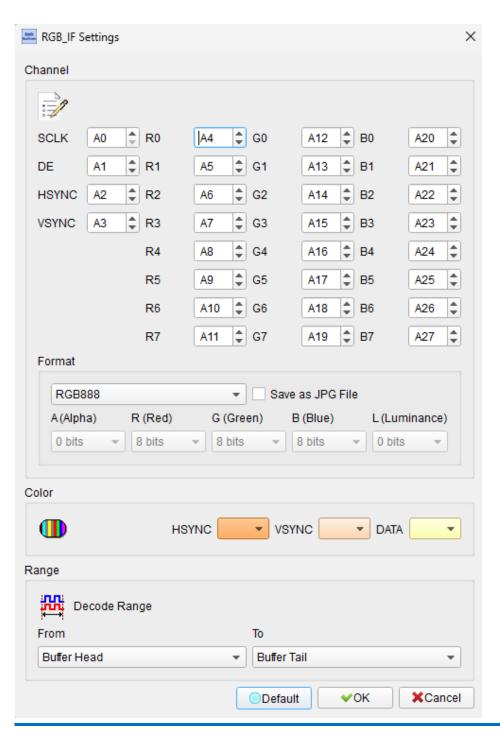

| RGB Interface  | 221 |

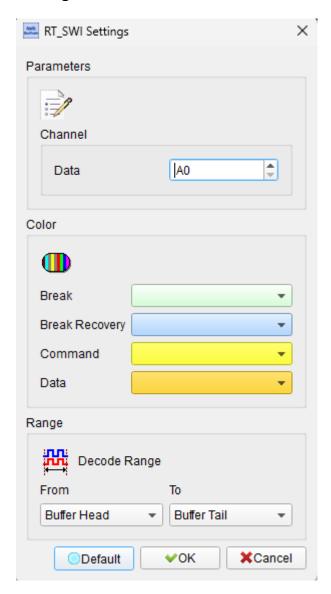

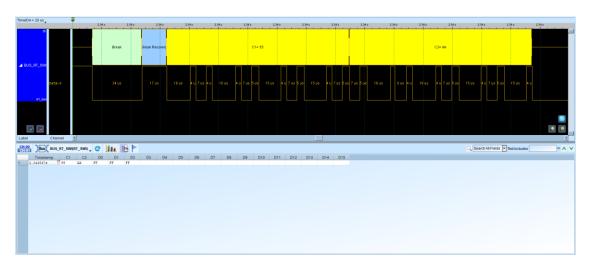

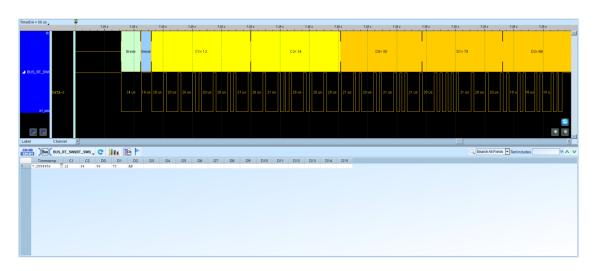

| RT_SWI         | 223 |

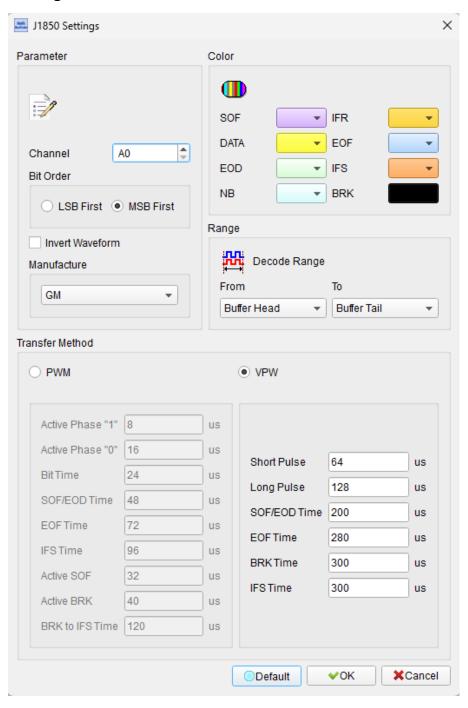

| SAE J1850      | 225 |

| S/PDIF         | 228 |

| SDIO           | 230 |

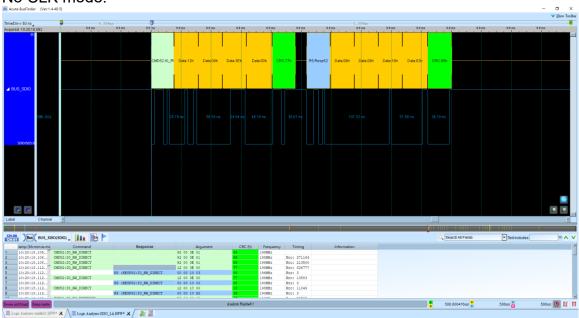

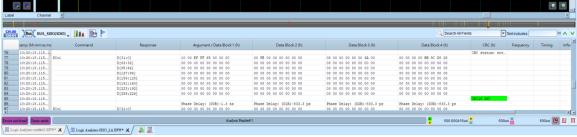

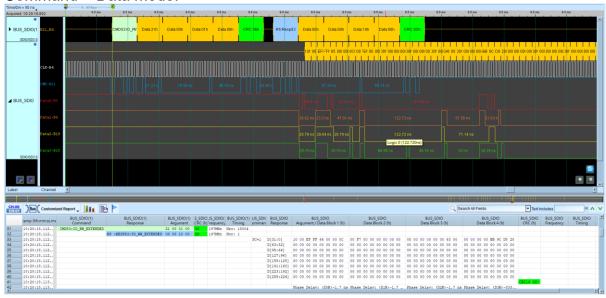

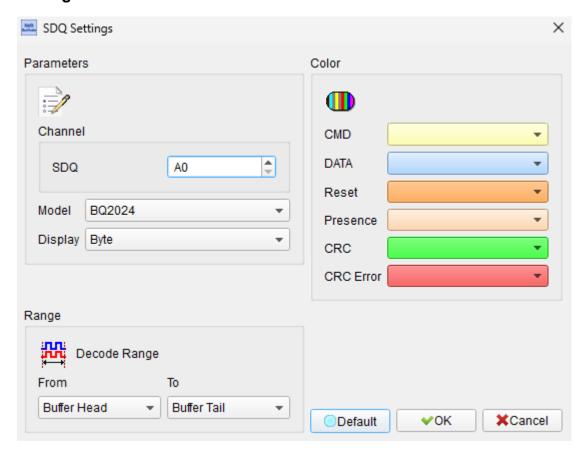

| SDQ            | 235 |

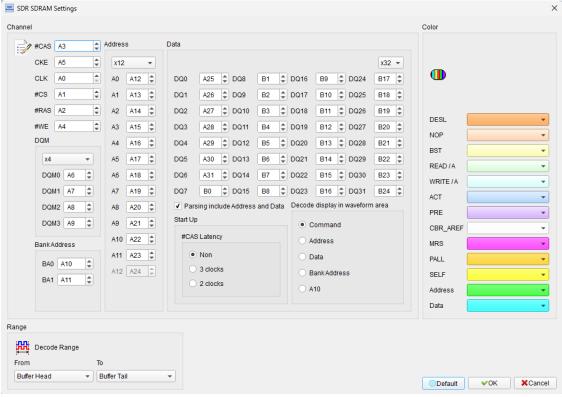

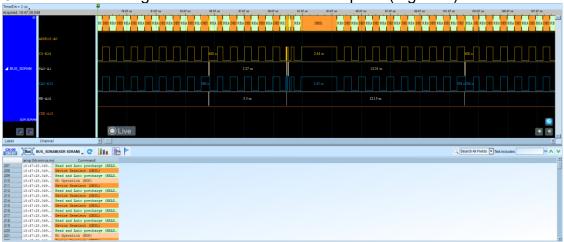

| SDR SDRAM      | 237 |

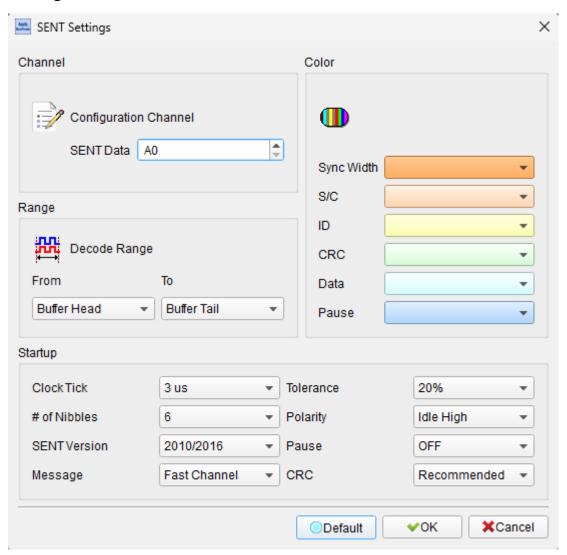

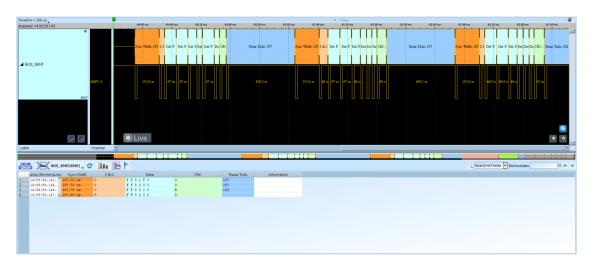

| SENT           | 240 |

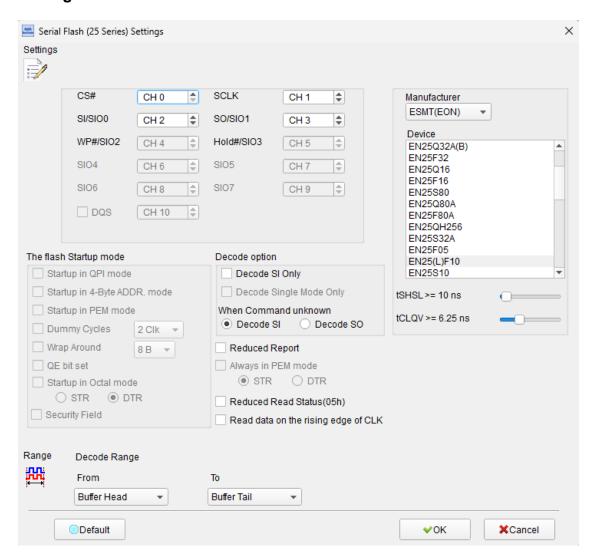

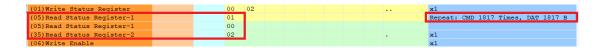

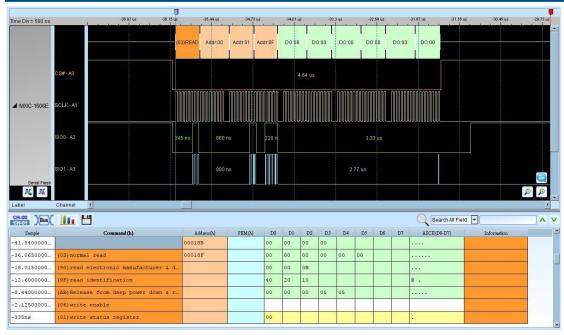

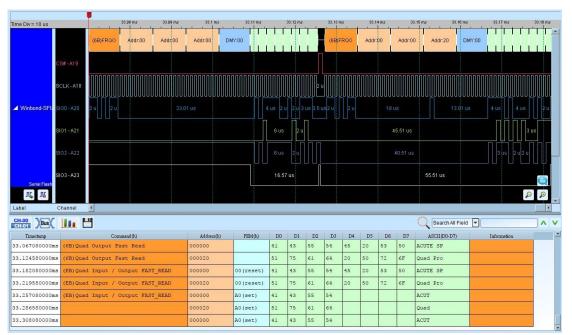

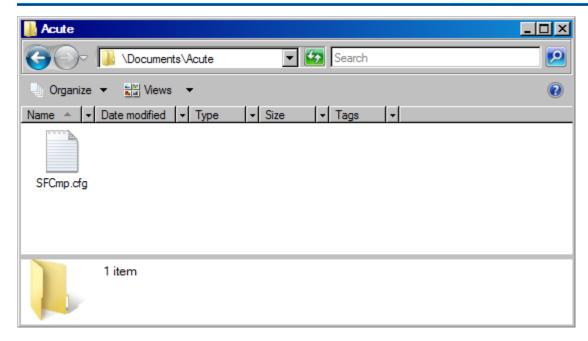

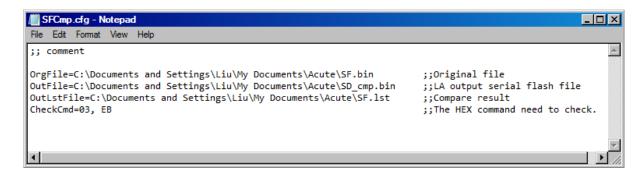

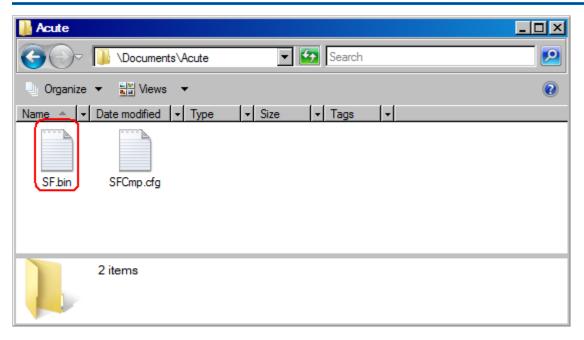

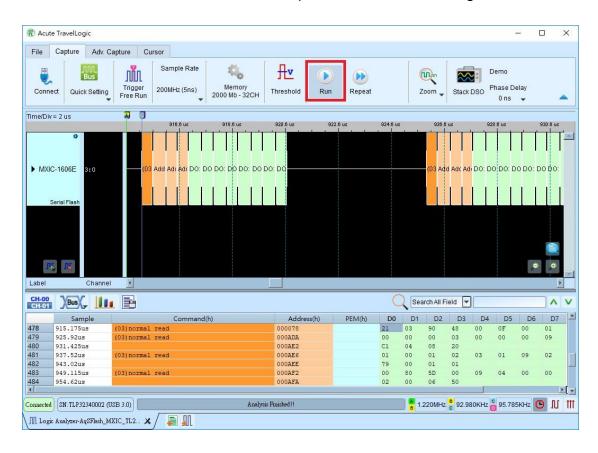

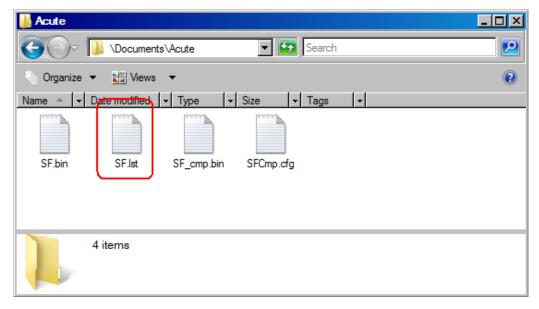

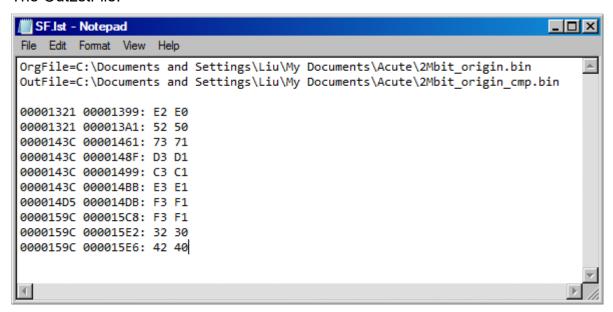

| Serial Flash   | 242 |

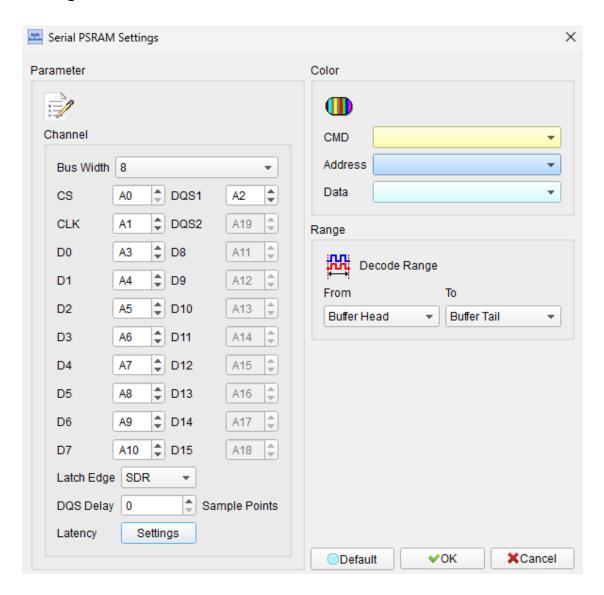

| Serial PSRAM   | 249 |

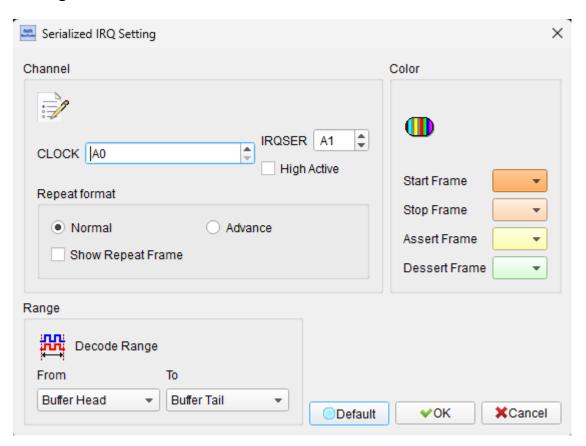

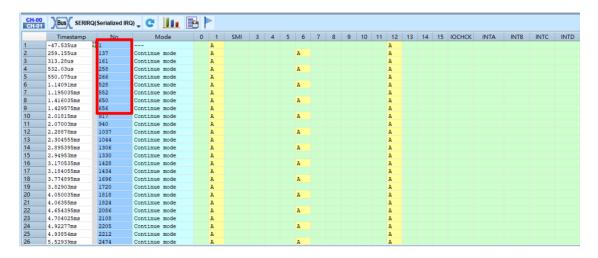

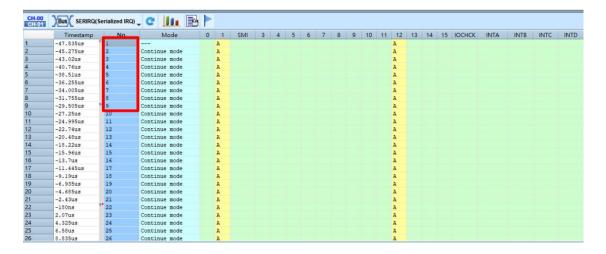

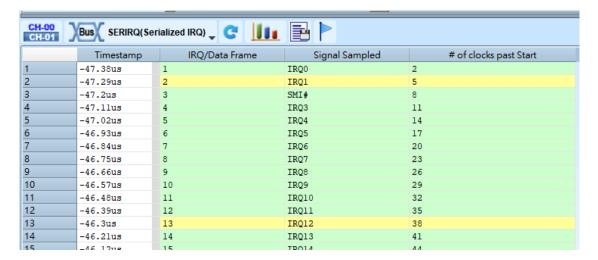

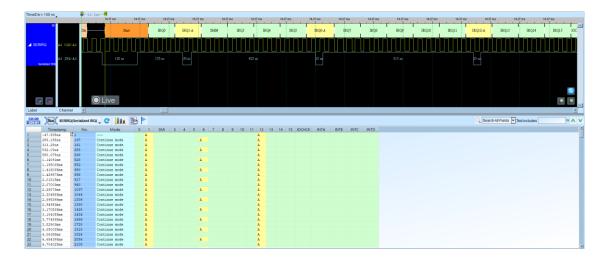

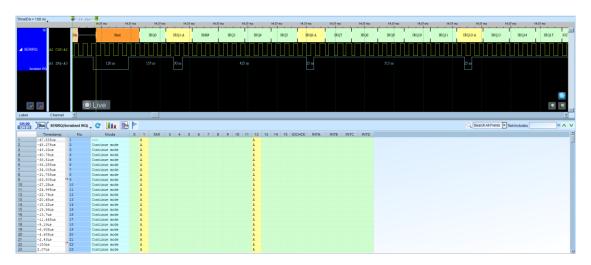

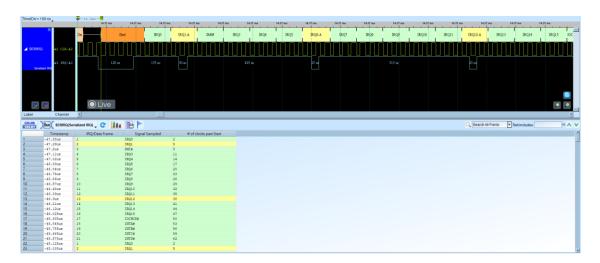

| Serialized IRQ          | 251 |

|-------------------------|-----|

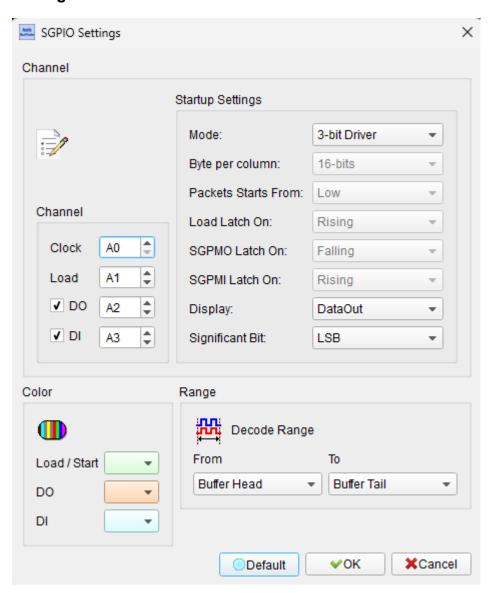

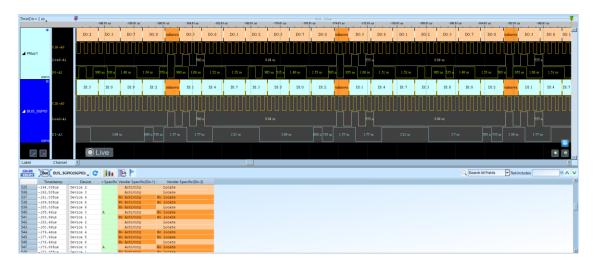

| SGPIO                   | 255 |

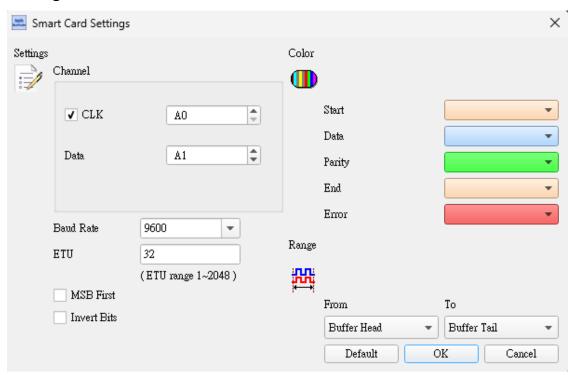

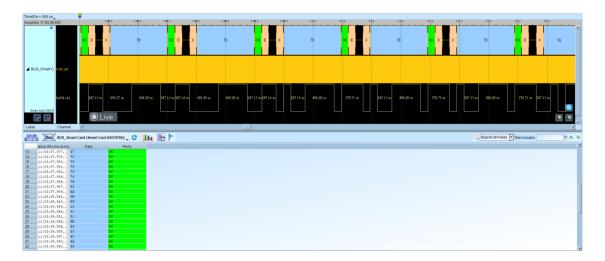

| Smart Card (ISO7816)    | 257 |

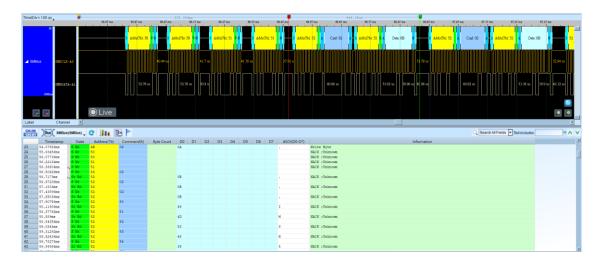

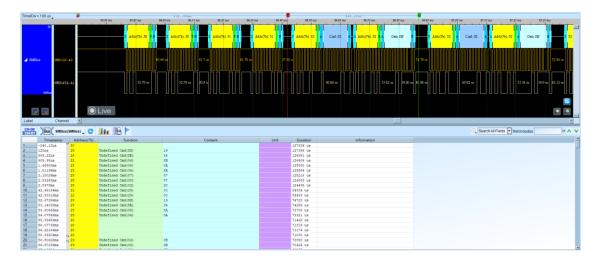

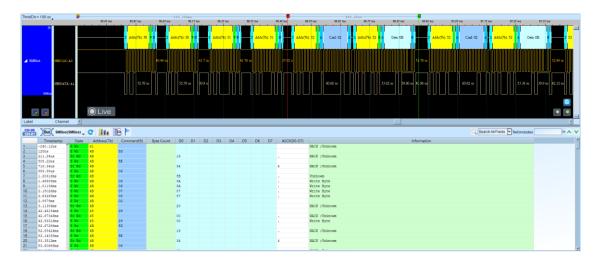

| SMBus                   | 259 |

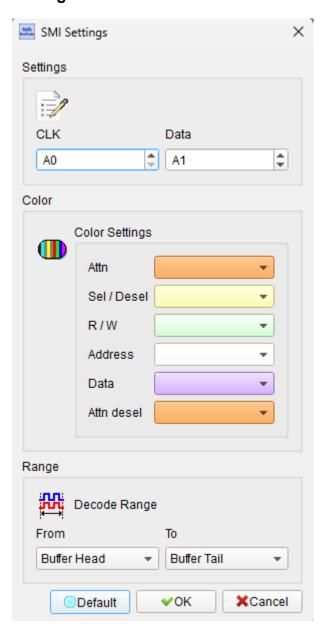

| SMI                     | 262 |

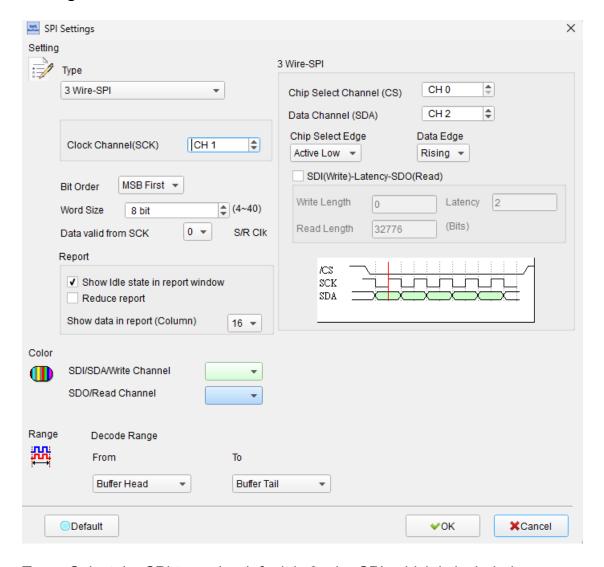

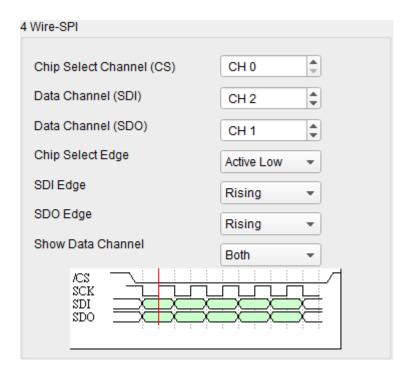

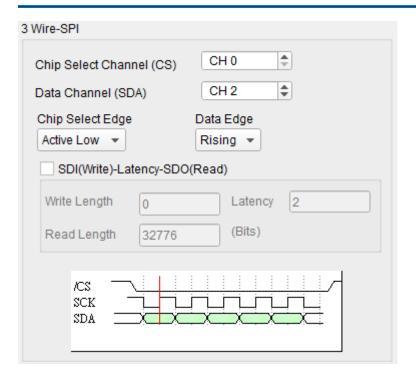

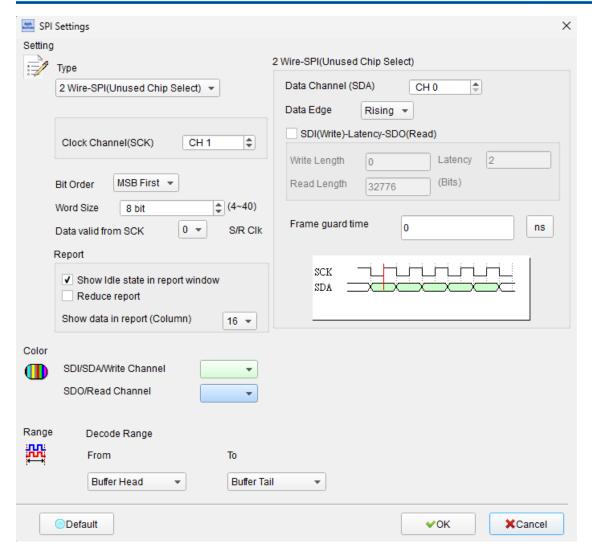

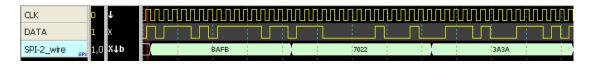

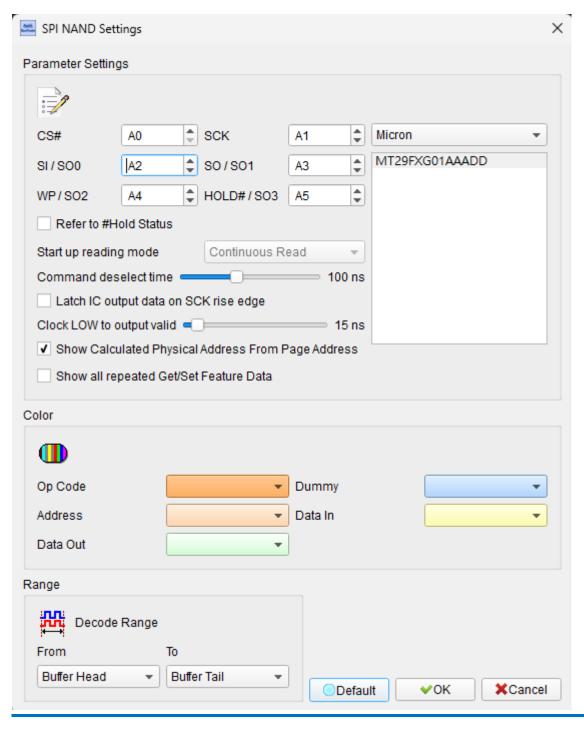

| SPI                     | 264 |

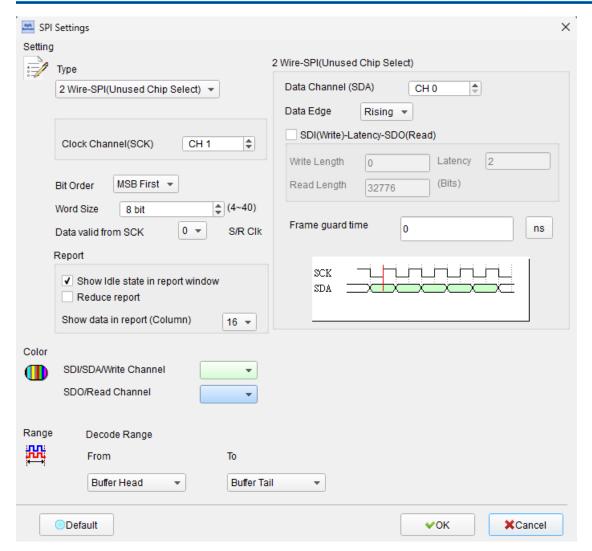

| SPI NAND                | 272 |

| SSI                     | 275 |

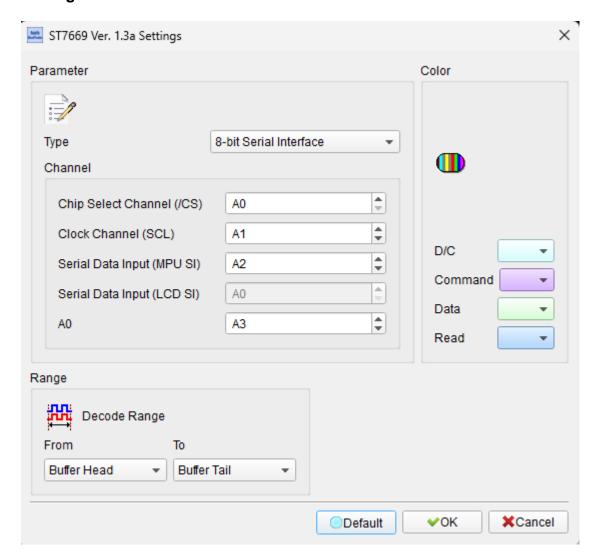

| ST7669                  | 277 |

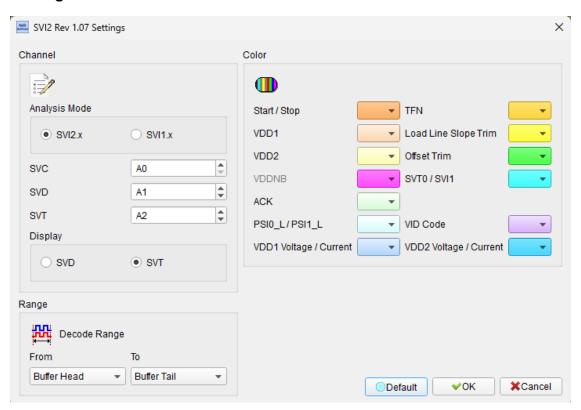

| SVI2                    | 279 |

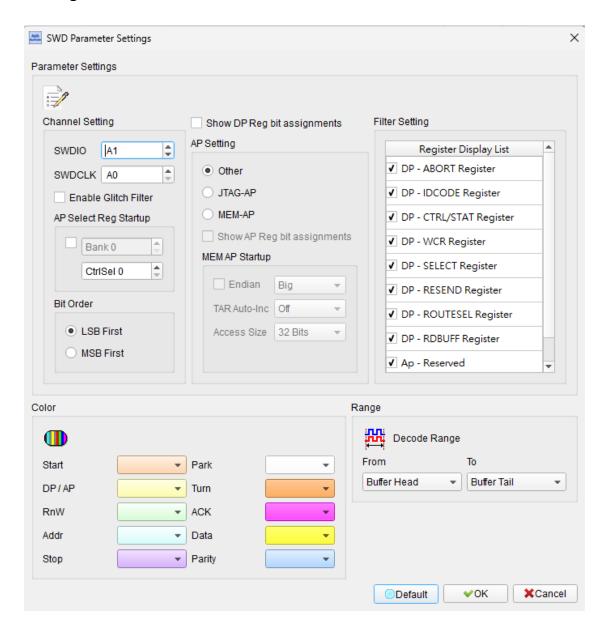

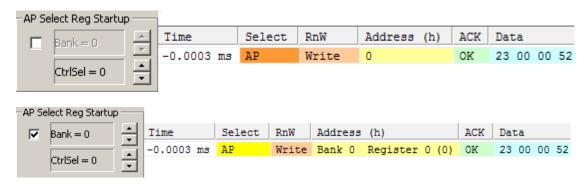

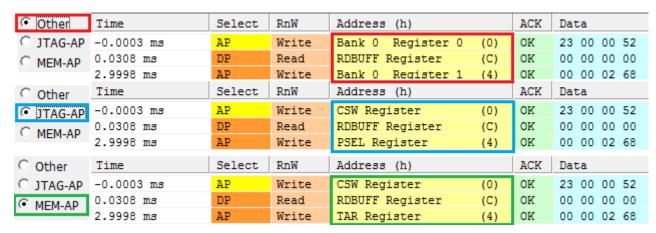

| SWD                     | 281 |

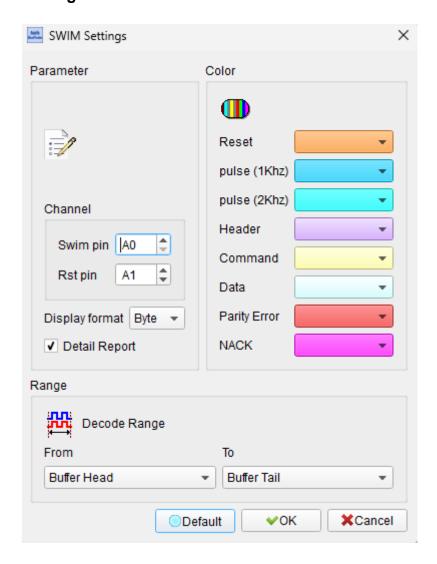

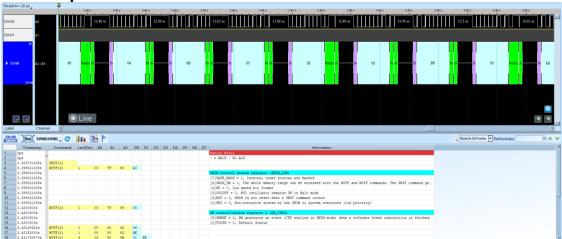

| SWIM                    | 285 |

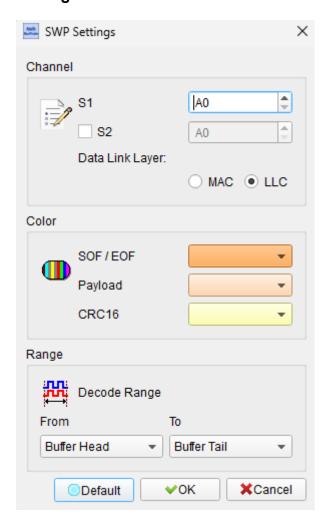

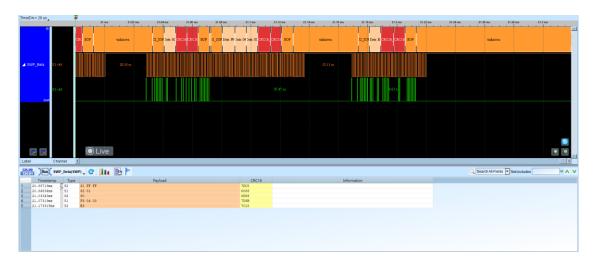

| SWP                     | 287 |

| TDM                     | 289 |

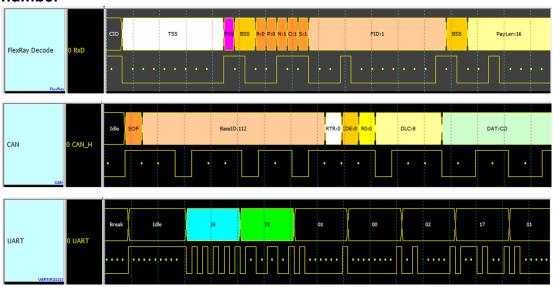

| UART(RS-232, RS485)     | 292 |

| UFCS                    | 295 |

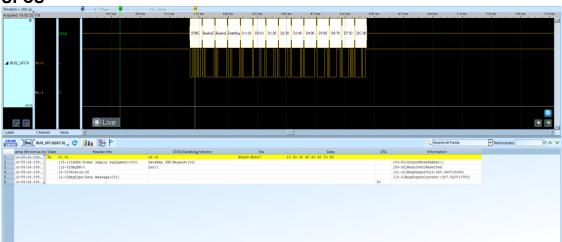

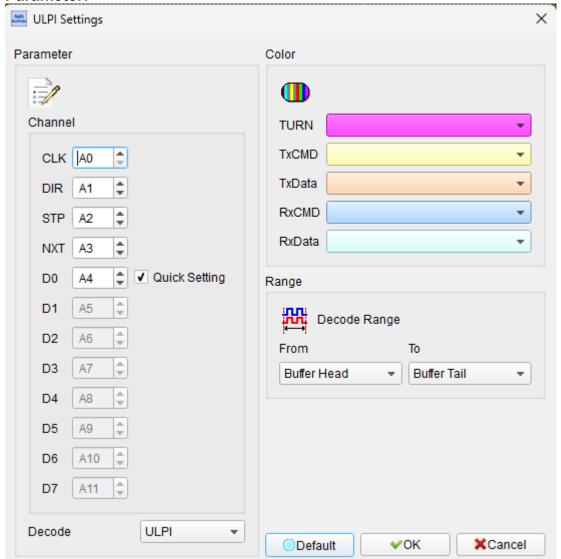

| ULPI                    | 297 |

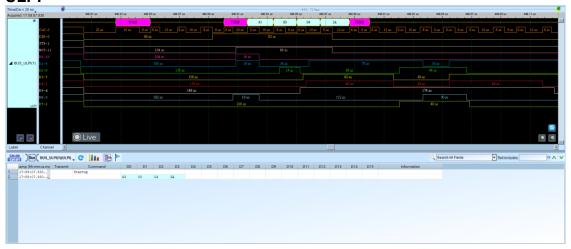

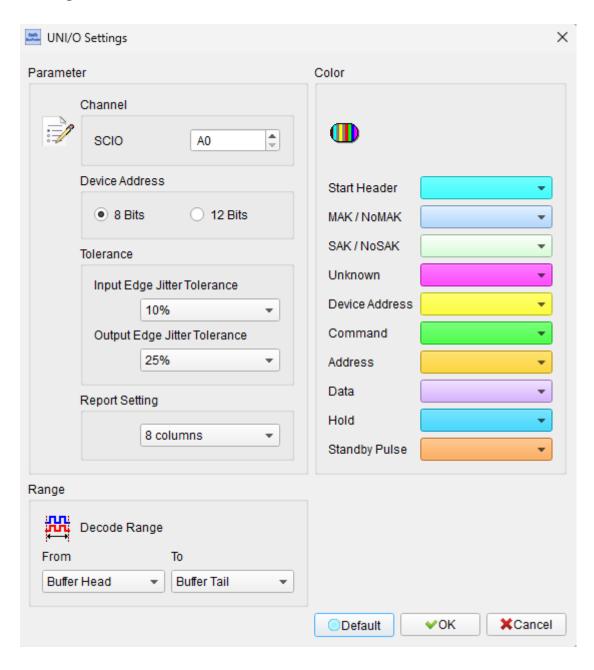

| UNI/O                   | 299 |

| USB PD                  | 301 |

| USB1.1                  | 304 |

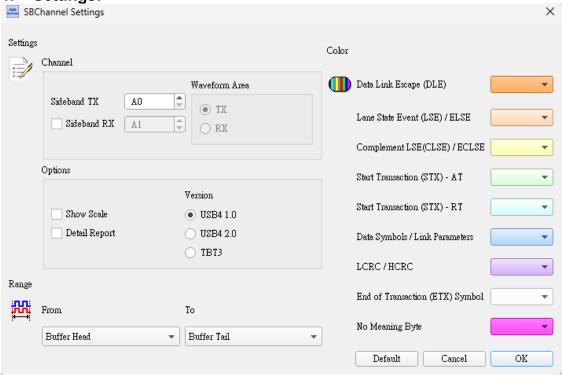

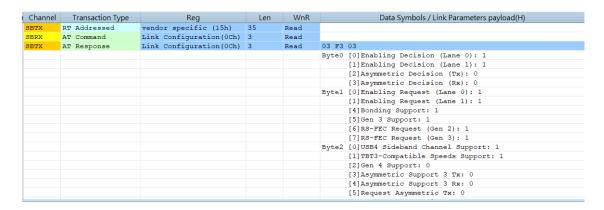

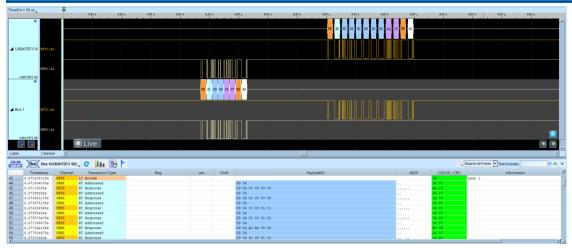

| USB4/TBT3 SB            | 306 |

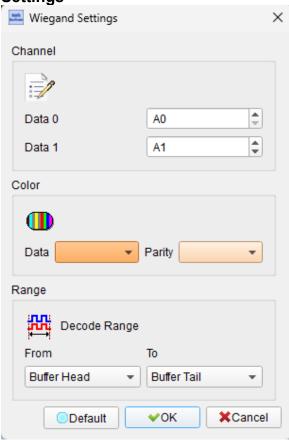

| Wiegand                 | 309 |

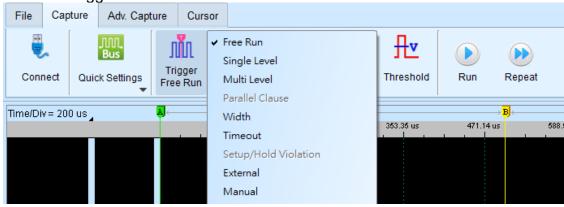

| Chapter 2 Bus Trigger   | 310 |

| Bus Trigger             | 310 |

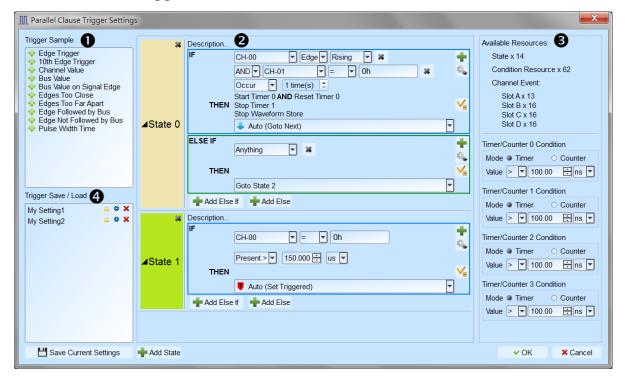

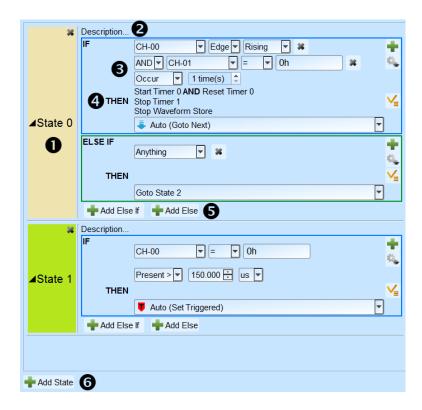

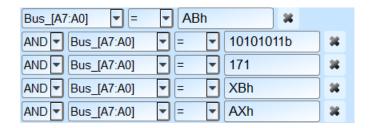

| Parallel Clause Trigger | 312 |

| Clause Trigger          |     |

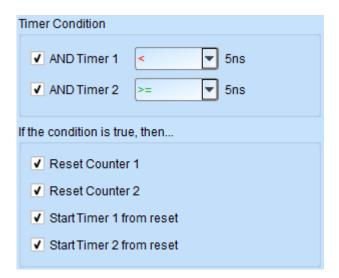

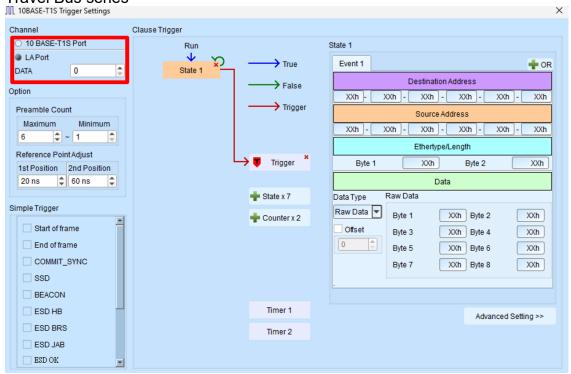

| 10BASE-T1S Trigger      | 320 |

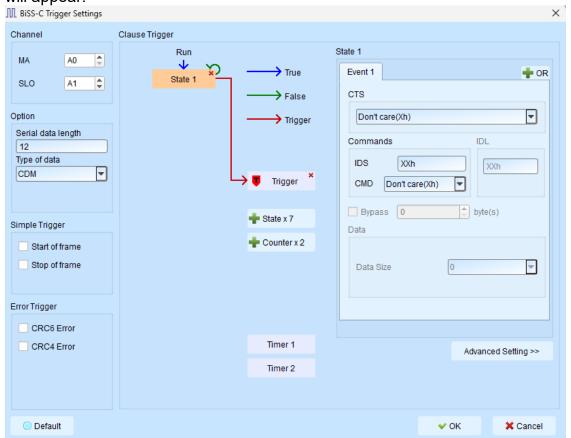

| BiSS-C Trigger                    | 322 |

|-----------------------------------|-----|

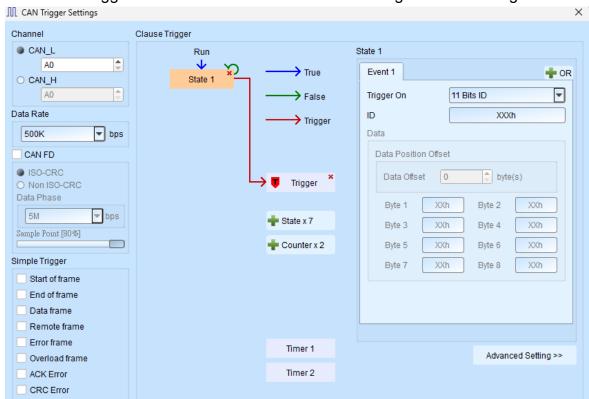

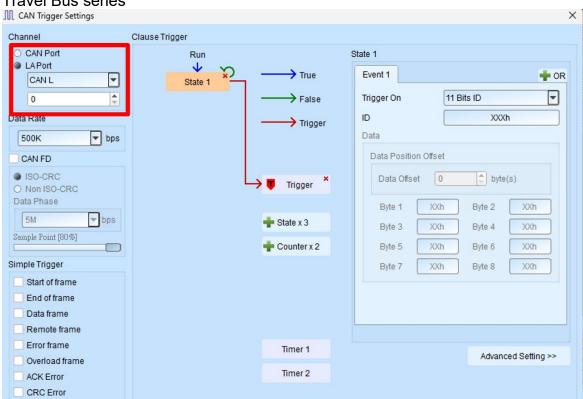

| CAN Trigger                       | 323 |

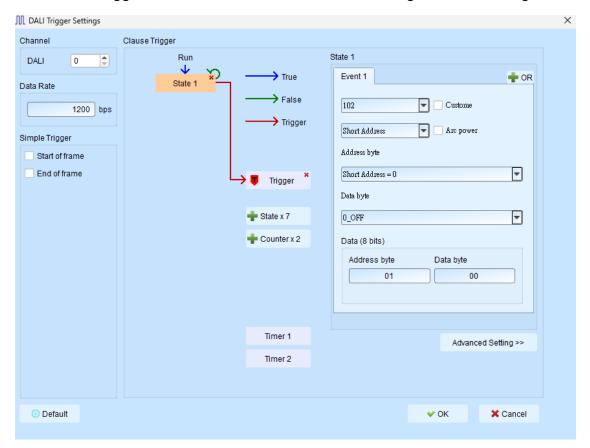

| DALI2 Trigger                     | 325 |

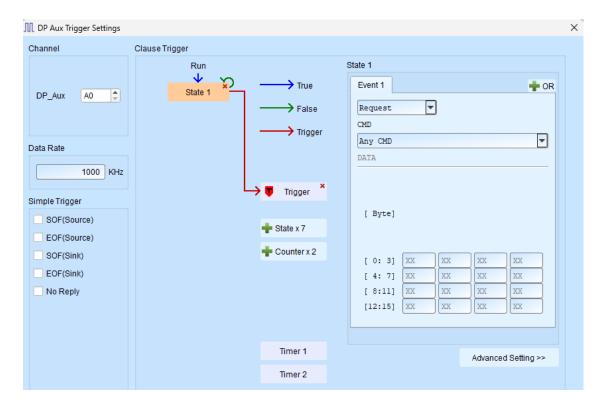

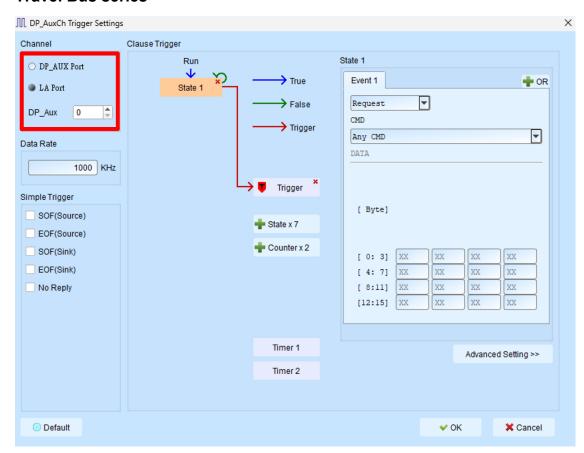

| DPAux Ch Trigger                  | 326 |

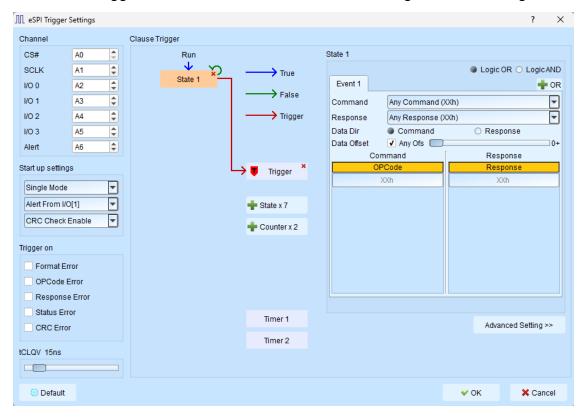

| eSPI Trigger                      | 328 |

| HIDoverl2C Trigger                | 330 |

| HyperBus Trigger                  | 332 |

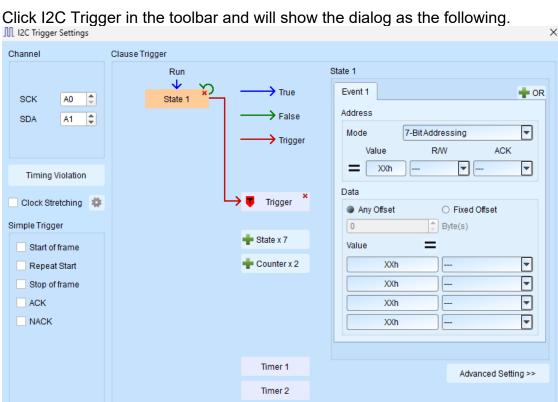

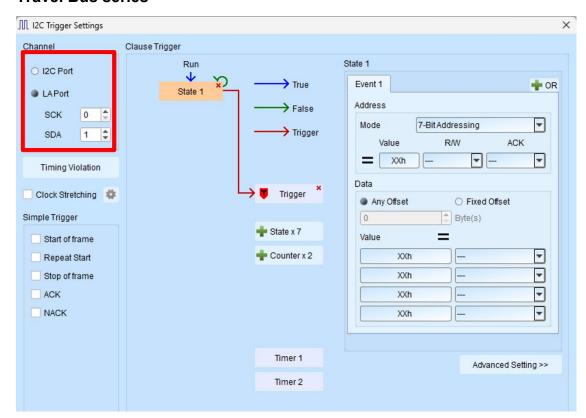

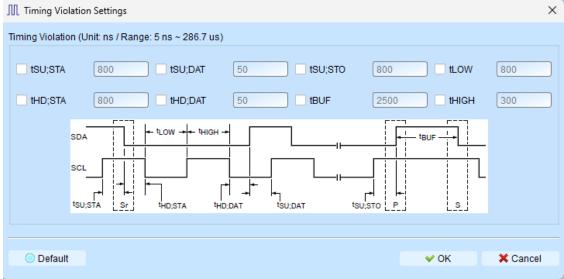

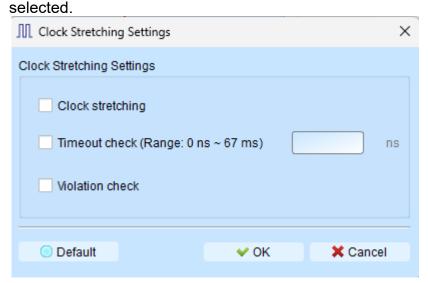

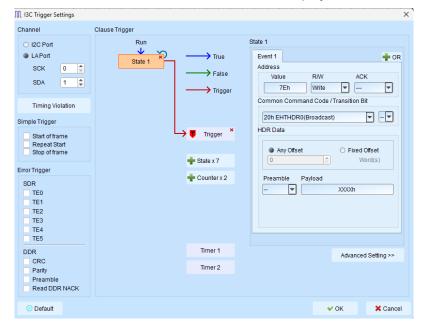

| I <sup>2</sup> C Trigger          | 334 |

| I <sup>2</sup> S Trigger          | 337 |

| LIN Trigger                       | 338 |

| LPC Trigger                       | 339 |

| MDIO Trigger                      | 340 |

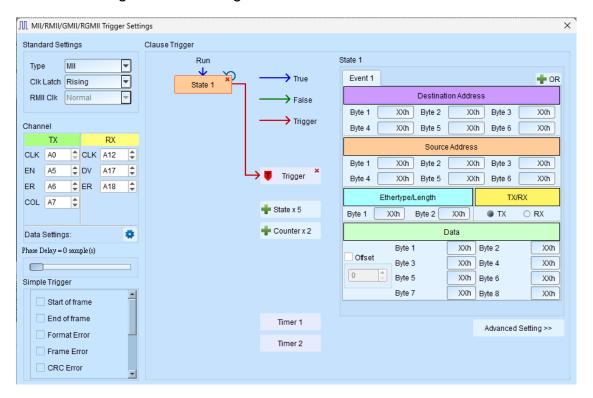

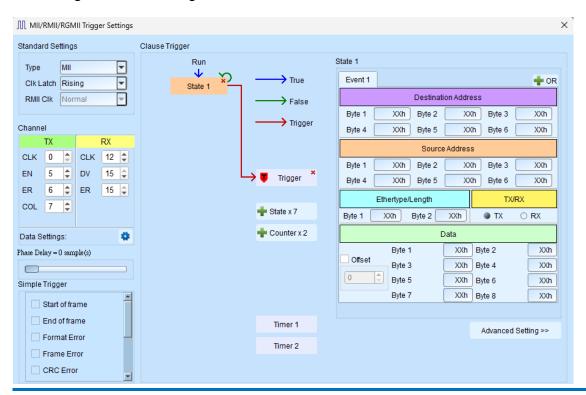

| MII / RMII / GMII / RGMII Trigger | 341 |

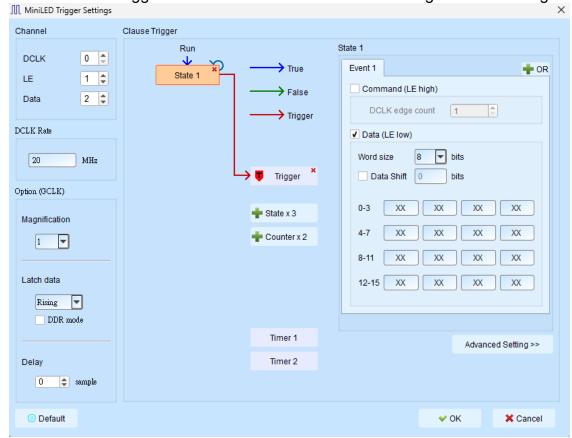

| MiniLED Trigger                   | 343 |

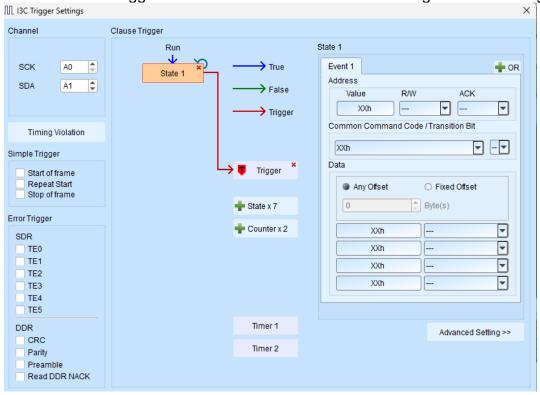

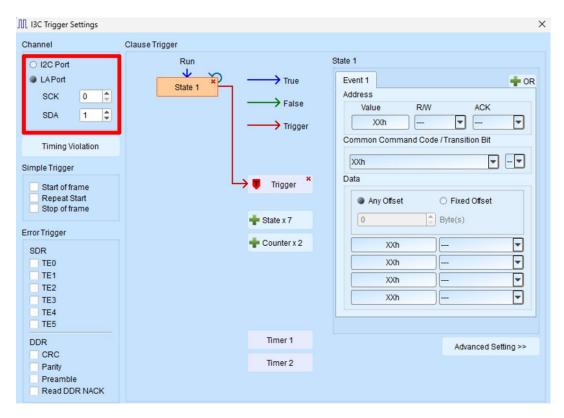

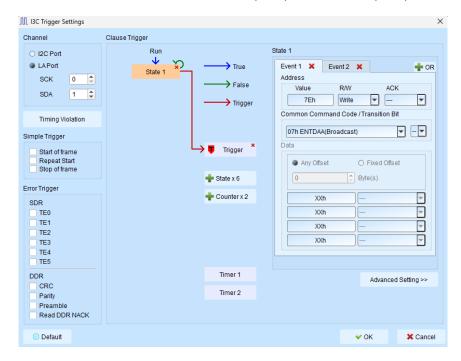

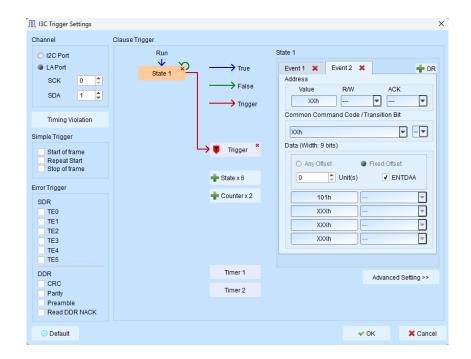

| MIPI I3C Trigger                  | 344 |

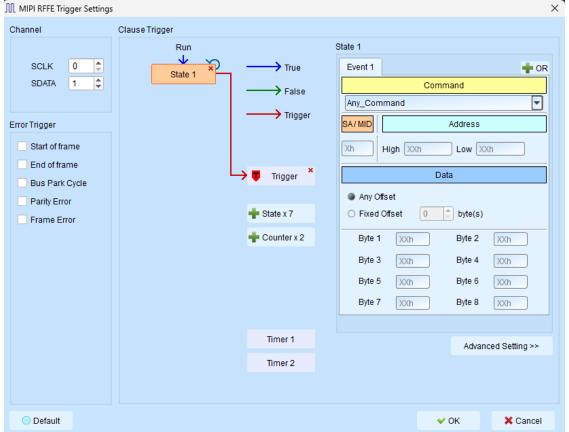

| MIPI RFFE Trigger                 | 347 |

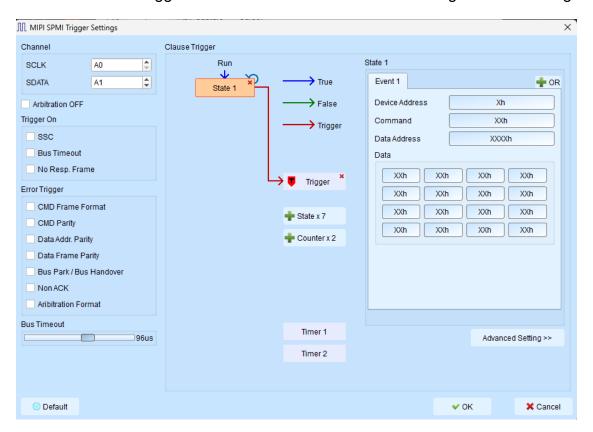

| MIPI SPMI Trigger                 | 348 |

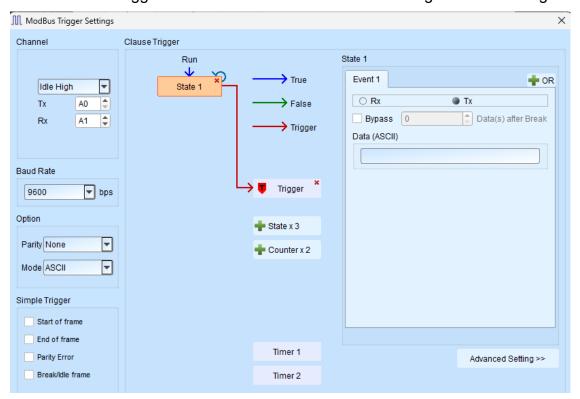

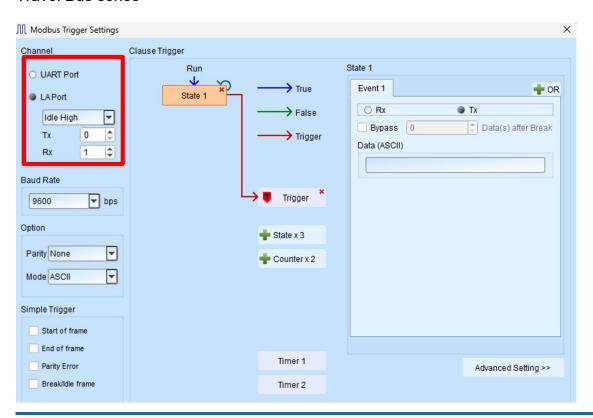

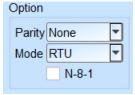

| ModBus Trigger                    | 349 |

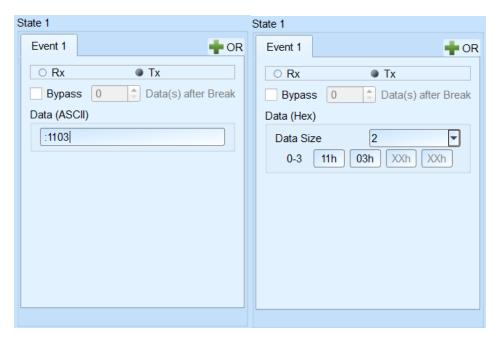

| NAND Flash Trigger                | 352 |

| PMBus Trigger                     | 356 |

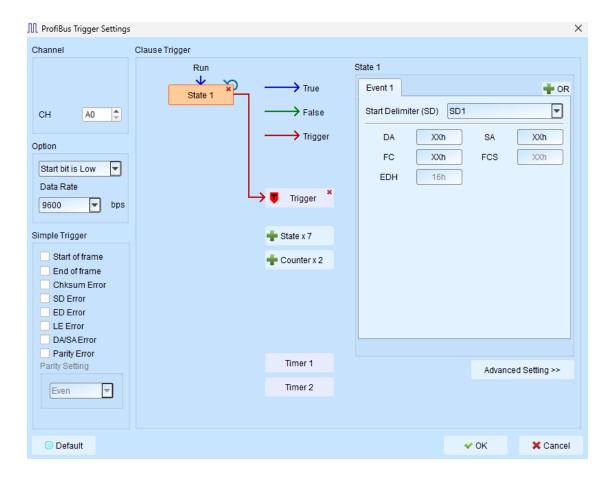

| ProfiBus Trigger                  | 358 |

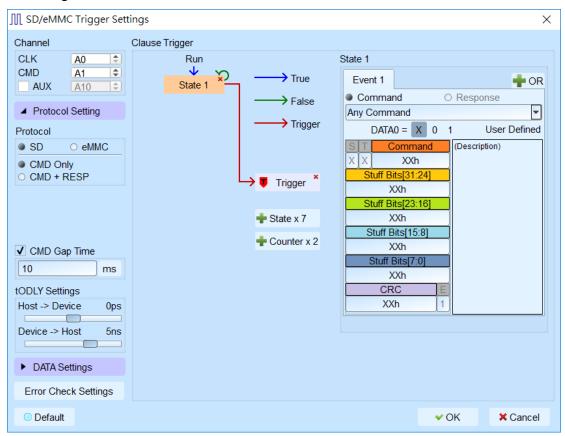

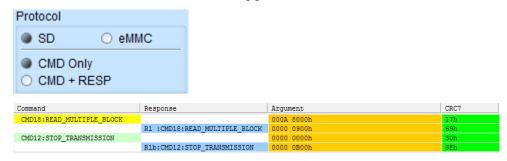

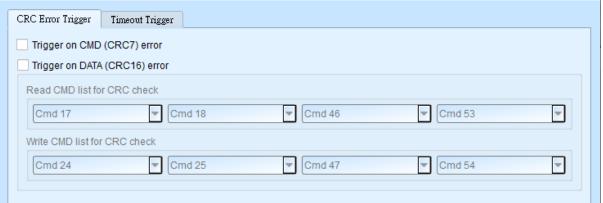

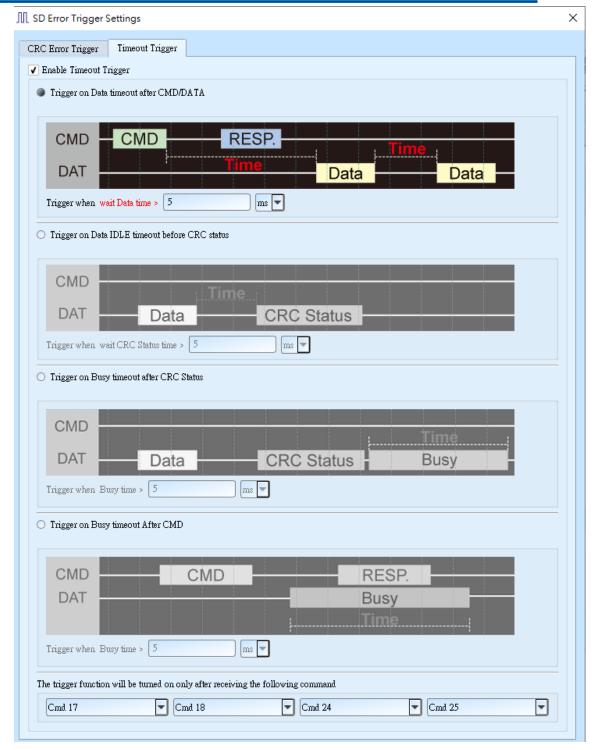

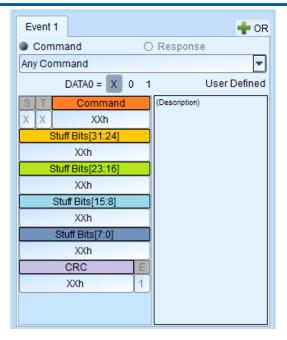

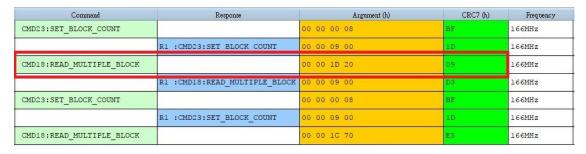

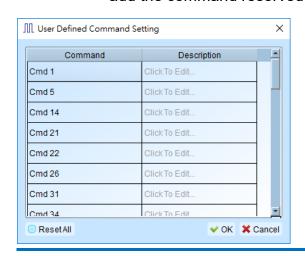

| SD/eMMC Trigger                   | 359 |

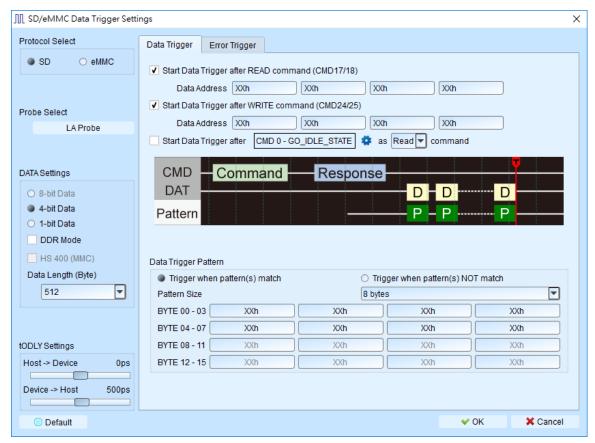

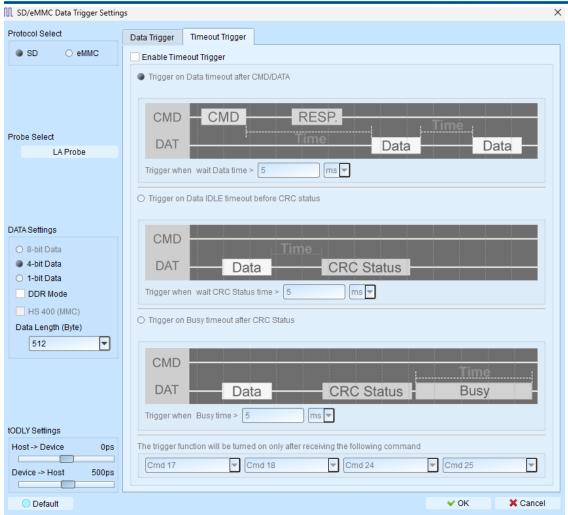

| SD/eMMC Data Trigger              | 363 |

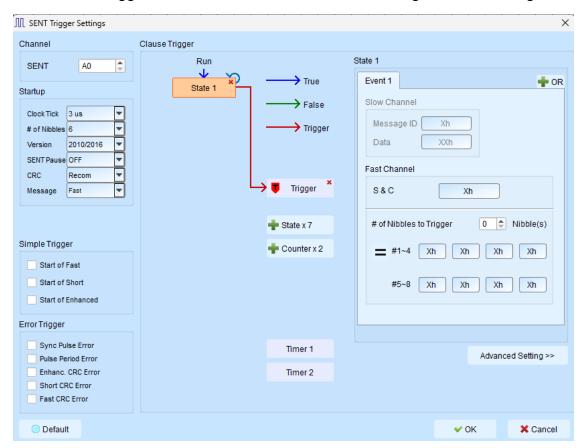

| SENT Trigger                      | 365 |

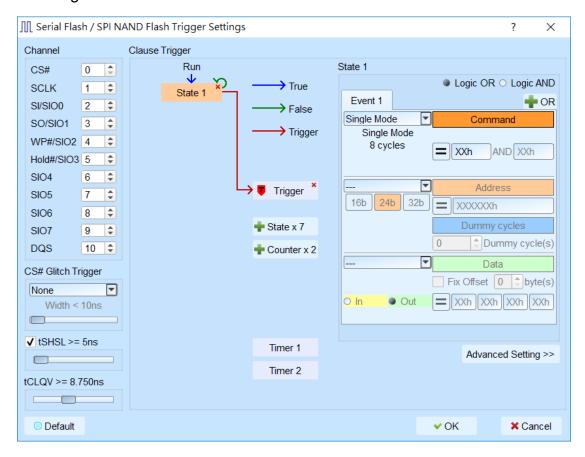

| Serial Flash / SPI NAND Trigger   | 366 |

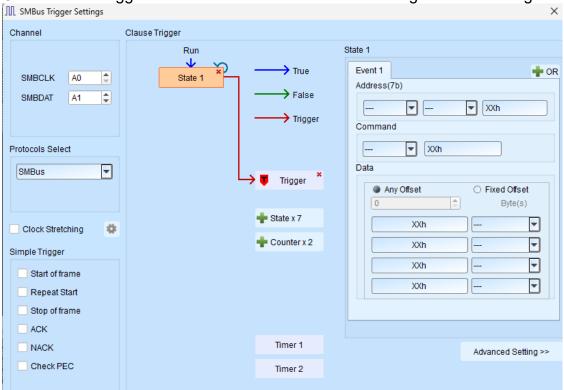

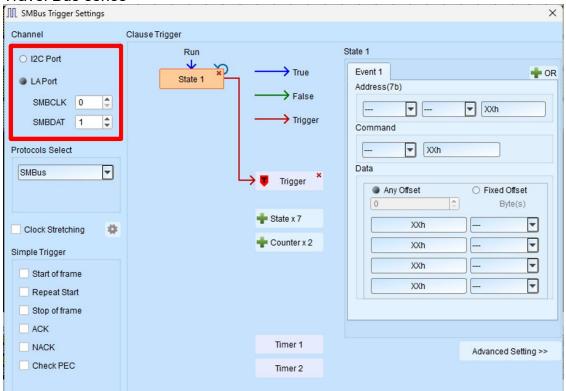

| SMBus Trigger                     | 367 |

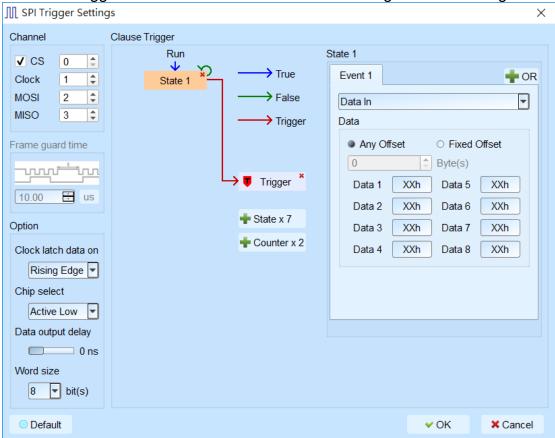

| SPI Trigger     | 369 |

|-----------------|-----|

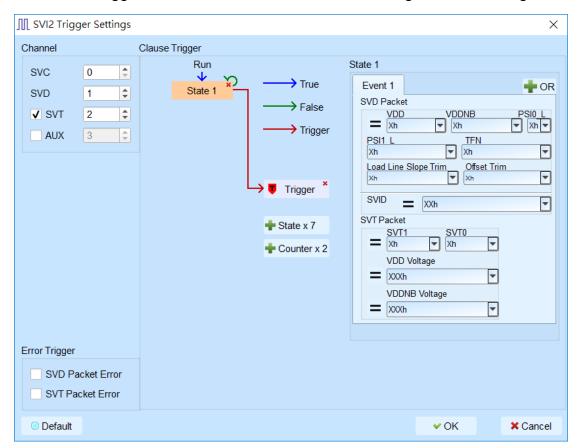

| SVI2 Trigger    | 371 |

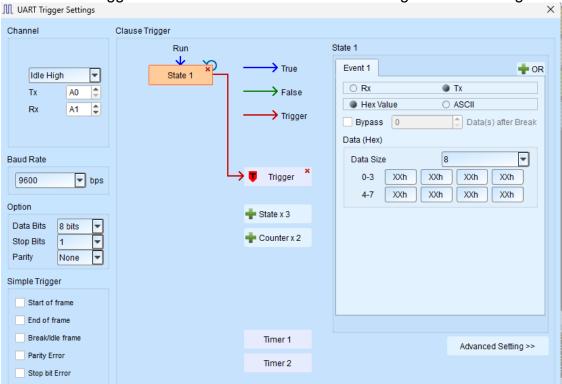

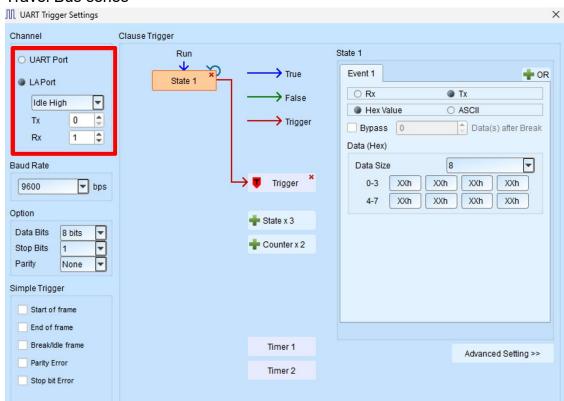

| UART Trigger    | 372 |

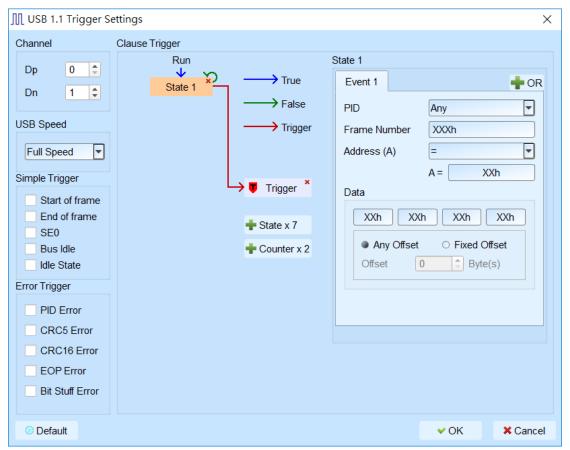

| USB 1.1 Trigger | 374 |

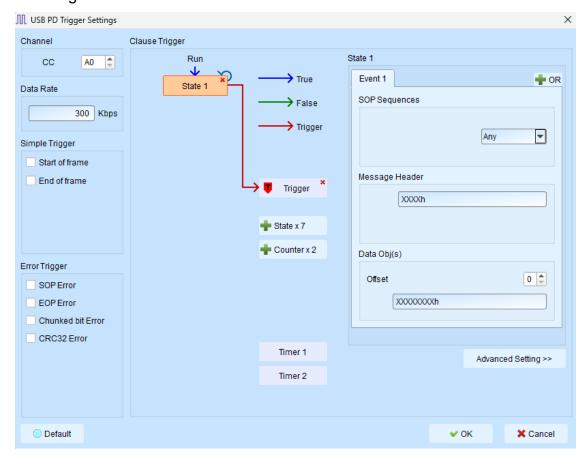

| USB PD Trigger  | 375 |

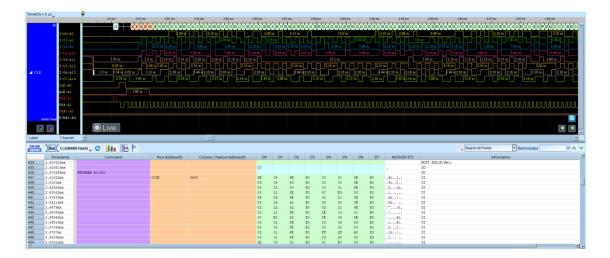

# Chapter 1 Bus Decode

# **Basic operation**

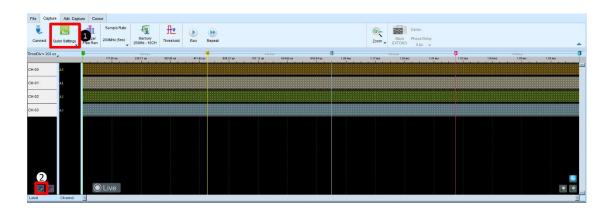

# Add a Bus Decode

# Method 1:

Click the Quick Setting in the menu (number 1 in the figure above), and select the bus decode.

### Method 2:

Click Add Bus Decode (number 2 int the figure above) in the Label menu or right-click the label field to show the dialog box.

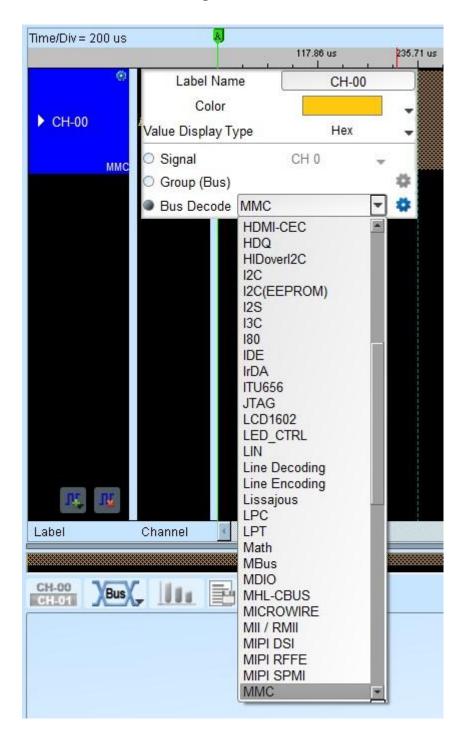

## Advance channel setting

- **1. Bus Name:** Enter the label name with 31 characters or less. (Chinese word expresses two characters.)

- 2. Color: Set the waveform color.

- 3. Display the waveforms with decode

- 4. Display the waveforms with its decode together.

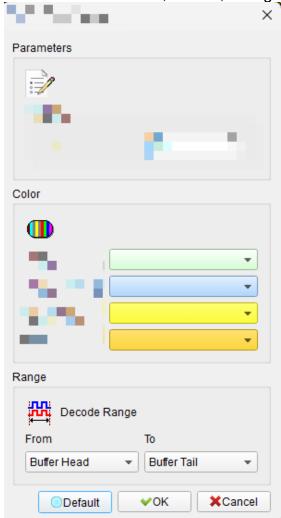

- 5. Advance:

Set the decode parameters or press **OK** to use default settings. There are "Channel"/"Parameter', "Color", "Range" settings

## **Specially Bus Decode**

The bus decodes display the data in text format, but some decodes are able to show the original form for the data such as voice (I2S decode...), image, analog waveform (ADC decode) etc.

UART/CAN/FlexRay..bus decodes (released since 2009/9, LA Viewer Ver2.0): The data is displayed according to bit points in order to calculate the bit number •

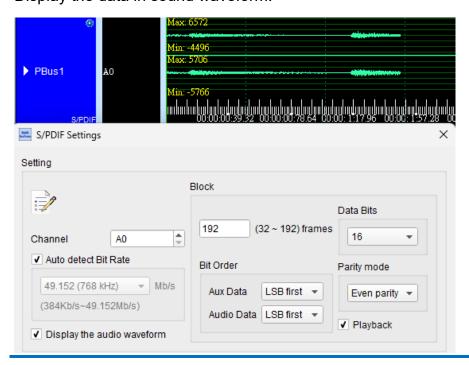

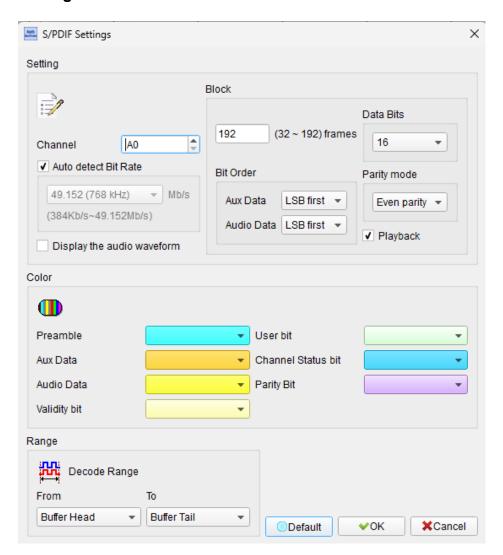

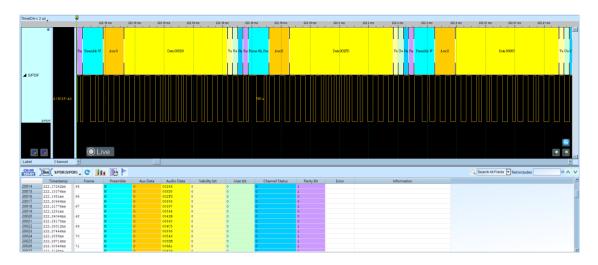

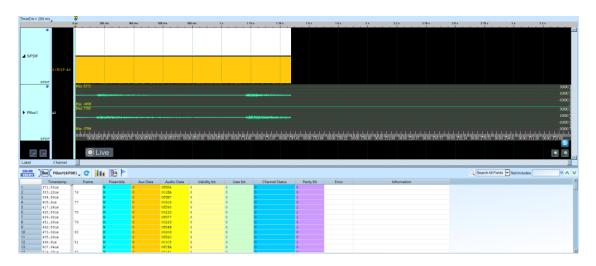

# S/PDIF analysis (released since 2010/11, LA Viewer Ver2.5):

Display the data in sound waveform.

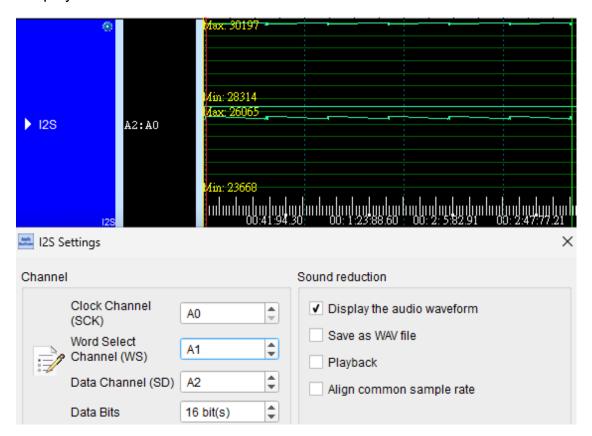

# l<sup>2</sup>S analysis (released since 2011/9, LA Viewer Ver2.6.3):

Display the data in sound waveform ∘

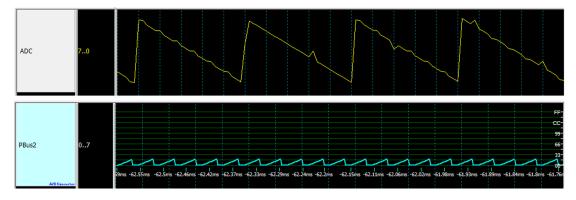

### ADC bus decode:

Display the input data in graph •

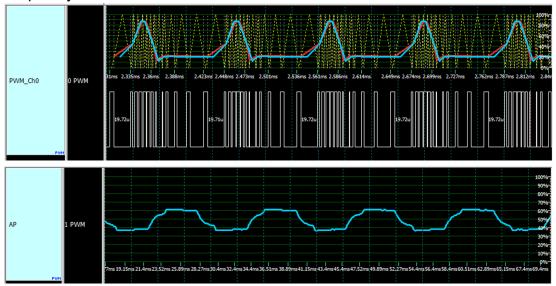

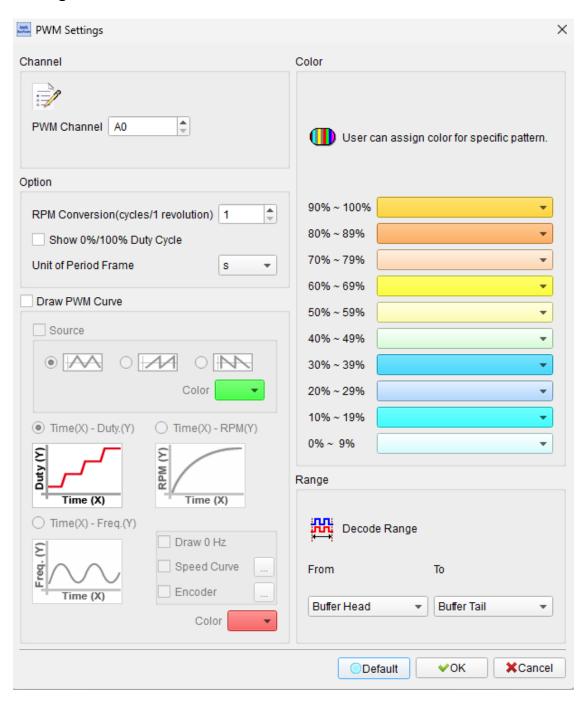

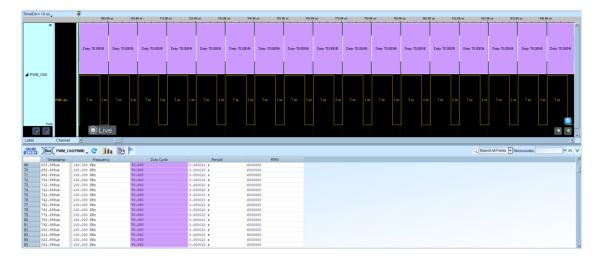

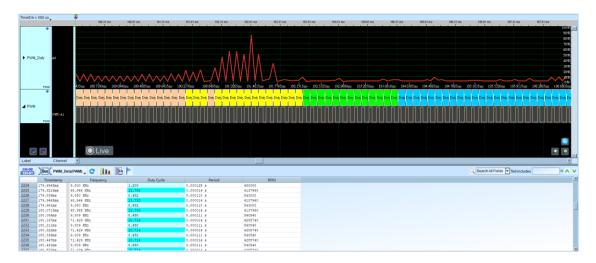

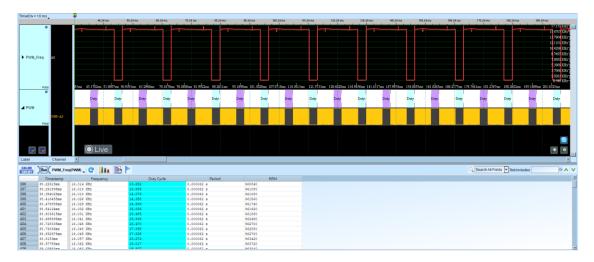

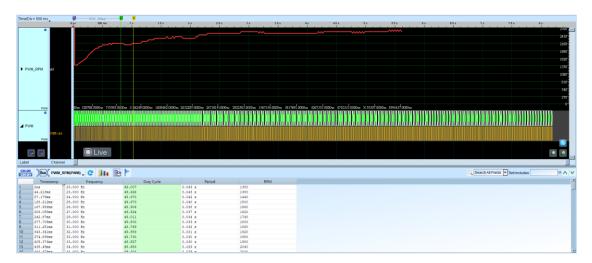

# PWM analysis (released since 2012/8, LA Viewer Ver2.7.3):

Restore and display the data in the waveform window as percentile or frequency  ${}^{\circ}\,$

# **Bus Decode Settings Introduction**

Please note: All are prefixed with 'Ch' except BusFinder or LA in the channel, which are prefixed with 'A'.

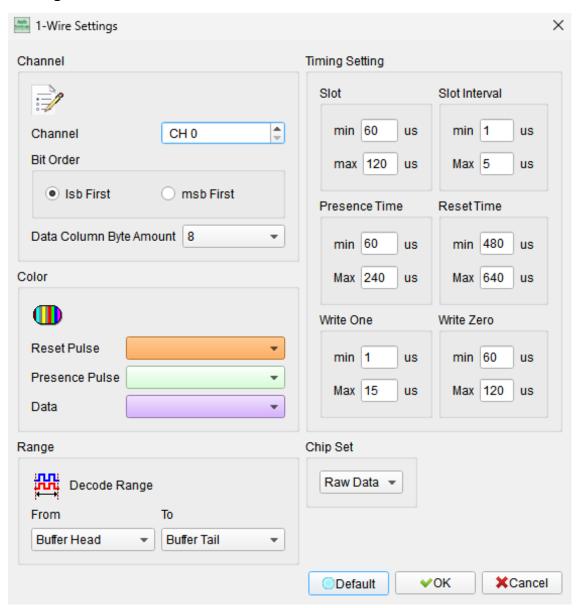

### 1-Wire

Developed by Dallas Semiconductor, the 1-Wire protocol defines several signal types such as Reset Pulse, Presence Pulse, Write 1, Write 0, Read 1, and Read 0, and combines these signal types into a command sequence. The transmission mode is LSB (Least-significant bit) to MSB (Most-significant bit), and the transmission speed is divided into Overdrive speed and Standard speed.

### **Settings**

Channel: Setting the Data Channel Source

Bit Order: Set whether the analyzed data is LSB first or MSB first.

**Data Byte Column Amount:** Set how many bytes of data are displayed in a row of the Data field in the Report area; user can select 8, 16, or 32.

# Timing Setting: all unit is us.

#### 1. Slot Time:

- I. Min: Set the minimum length of time of a slot.

- II. Max: Set the maximum length of time of a slot.

#### 2. Slot Interval:

- I. Min: Set the minimum length of time between each slot.

- II. Max: Set the maximum length of time between each slot.

#### 3. Reset Time:

- I. **Min:** Set the minimum length of time that the waveform will be pulled down when is in Reset.

- II. **Max:** Set the maximum length of time that the waveform will be pulled down when is in Reset.

#### 4. Presence Time:

- I. **Min:** Set the minimum length of time that the waveform will be pulled down when is in Presence.

- **II. Max:** Set the maximum length of time that the waveform will be pulled down when is in Presence.

### 5. Write One:

- I. **Min:** Set the minimum length of time that the waveform will be pulled down when 1 is written.

- **II. Max:** Set the maximum length of time that the waveform will be pulled down when 1 is written.

### 6. Write Zero:

- I. **Min:** Set the minimum length of time that the waveform will be pulled down when 0 is written.

- **II. Max:** Set the maximum length of time that the waveform will be pulled down when 0 is written.

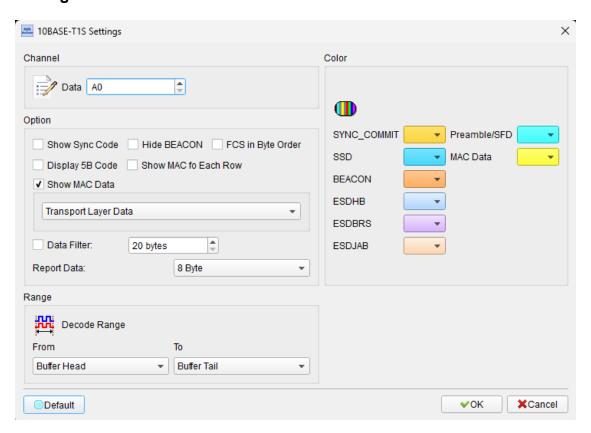

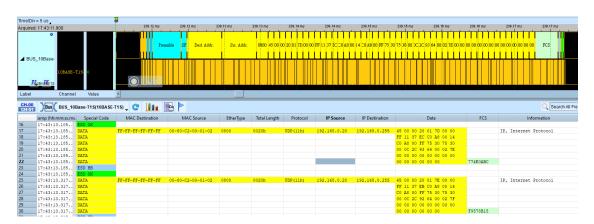

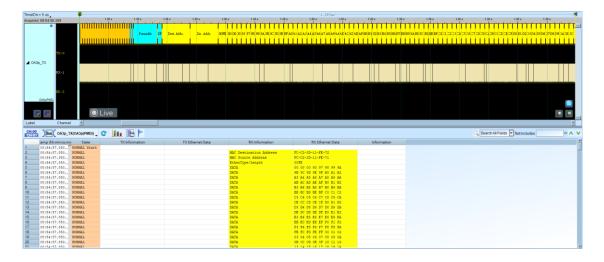

#### 10BASE-T1S

10Base-T1S uses Differential Manchester Encoding (DME). DME encodes data based on whether there is a transition within the clock period, indicating the logical state of the signal. If there is no transition within the clock period, the data state is logical 0. If transitions (either positive or negative) occur within the clock period, the data state is logical 1.

10BASE-T1S operates in a half-duplex bus configuration with a maximum length of 25 meters. It supports multipoint connections with two to eight nodes. The "S" in the standard name denotes short-range implementation. The intended use of 10BASE-T1S is to replace existing bus architectures that often result in "communication islands," such as CAN, CAN FD, LIN, and RS-485.

### Settings:

**Show Sync Code:** Show Commit, SSD in report; enabled when checked. Hide BEACON: Hide Beacon data is not shown; enabled when checked.

FCS in Byte order: Present FCS in report in byte order; enabled when

checked.

Display 5B Code: Show special code value

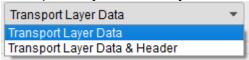

# Show MAC Data: Show MAC Packet.

In IPv4(0800h), there will be 20bytes header. The Data column is able to show Transport Layer Data only or including the header.

### **Transport Layer Data:**

| Total Length | Protocol | IP Source    | IP Destination | Data                    |  |  |  |

|--------------|----------|--------------|----------------|-------------------------|--|--|--|

|              |          |              |                |                         |  |  |  |

| 0020h        | UDP(11h) | 192.168.0.20 | 192.168.0.255  | 75 30 75 30 00 0C 2C 93 |  |  |  |

|              |          |              |                | 64 00 02 7E 00 00 00 00 |  |  |  |

|              |          |              |                | 00 00 00 00 00 00 00 00 |  |  |  |

|              |          |              |                | 00 00                   |  |  |  |

# Transport Layer Data & Header:

| Total Length | Protocol | IP Source    | IP Destination | Data                    |  |  |  |

|--------------|----------|--------------|----------------|-------------------------|--|--|--|

| 0020h        | UDP(11h) | 192.168.0.20 | 192.168.0.255  | 45 00 00 20 01 7B 00 00 |  |  |  |

|              |          |              |                | FF 11 37 EE CO A8 00 14 |  |  |  |

|              |          |              |                | CO A8 00 FF 75 30 75 30 |  |  |  |

|              |          |              |                | 00 0C 2C 95 64 00 02 7C |  |  |  |

|              |          |              |                | 00 00 00 00 00 00 00 00 |  |  |  |

|              |          |              |                | 00 00 00 00 00 00       |  |  |  |

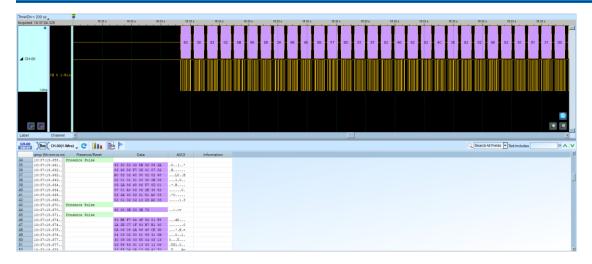

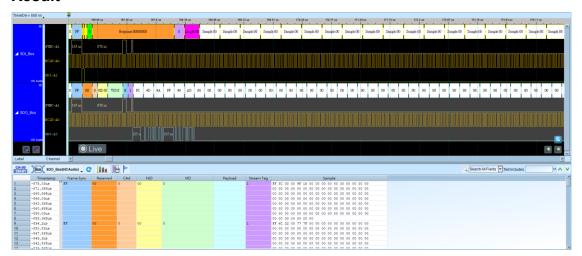

# Results:

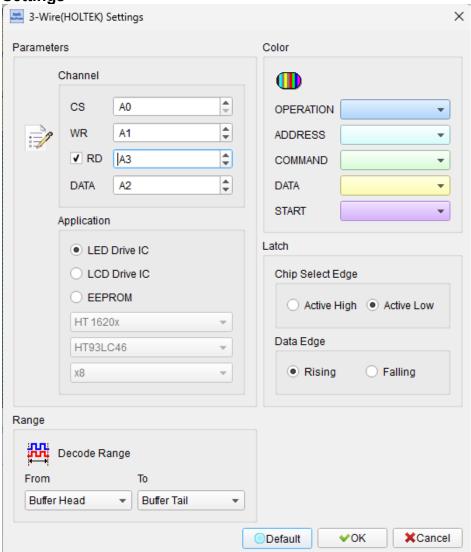

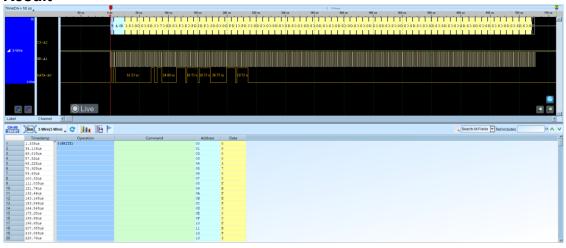

### 3-Wire

3-Wire protocol is established by HOLTEK SEMICONDUCTOR INC. It's Applied to control LED/LCD driver IC or EEPROM.

# **Settings**

Channel: Show the selected channels (CS:CH0, WR:CH1, DATA:CH2,

RD:CH3)

**LED Driver IC:** Select LED driver IC application. **LCD Driver ID:** Select LCD driver IC application.

**EEPROM:** Select EEPROM application.

Active High: Select Active High.

Active Low: Select low chip select (CS).

Rising: Select Rising Data Edge.

# Falling: Select Falling Data Edge.

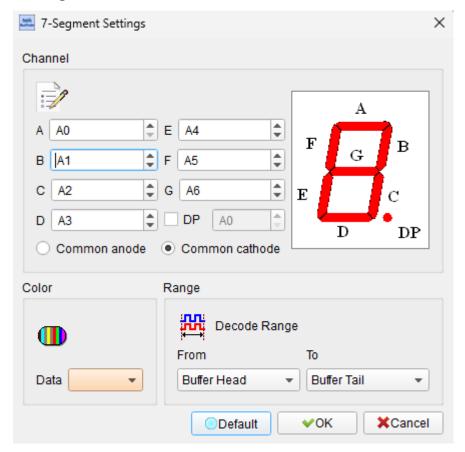

# 7-Segment

A seven-segment display, is a form of electronic display device for displaying decimal numerals that is an alternative to the more

complex dot-matrix displays.

|   | LED              | A   | В   | С   | D   | E   | F   | G   |

|---|------------------|-----|-----|-----|-----|-----|-----|-----|

| 0 | F G B  E D C  DP | ON  | ON  | ON  | ON  | ON  | ON  | OFF |

| 1 | F G B C DP       | OFF | ON  | ON  | OFF | OFF | OFF | OFF |

| 2 | F G B C DP       | ON  | ON  | OFF | ON  | ON  | OFF | ON  |

| 3 | F G B C DP       | ON  | ON  | ON  | ON  | OFF | OFF | ON  |

| 4 | F G B  E C  D DP | OFF | ON  | ON  | OFF | OFF | ON  | ON  |

| 5 | F G B C DP       | ON  | OFF | ON  | ON  | OFF | ON  | ON  |

| 6 | F G B            | ON  | OFF | ON  | ON  | ON  | ON  | ON  |

| 7 | F G B C DP       | ON  | ON  | ON  | OFF | OFF | OFF | OFF |

| 8 | F G B  E D C  DP | ON  |

| 9 | F G B C D DP     | ON  | ON  | ON  | ON  | OFF | ON  | ON  |

# **Settings**

**Channel:** Show the selected channel (CH 0).

**DP**: to analysis decimal point.

Common cathode/anode: Show the same cathode or anode.

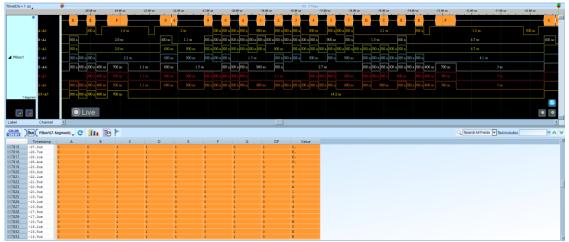

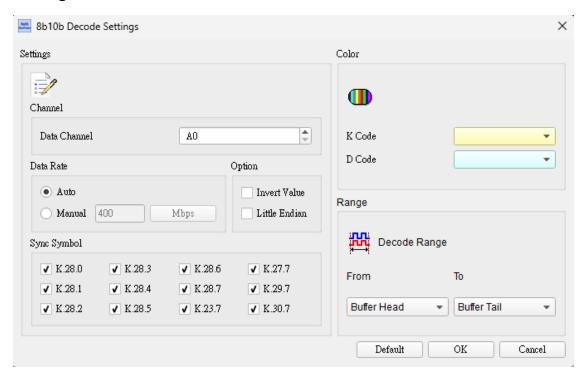

## 8b10b Decoding

8b/10b encoding is a coding technique commonly used in high-speed digital communications to convert every 8 bits of data into a 10 bits format. It was first invented by IBM in the 1980s to improve the reliability and stability of data transmission.

### Setting

**Data Channel:** Set the signal on the DUT to the channel number of the logic analyzer.

(LVDS signals need to be converted into single-ended signals or use LVDS probes)

**Data Rate:** User can set the data rate manually, or choose the 'Auto', let software calculate the data rate automatically.

### Option:

Invert Value: Invert the waveform.

Little Endian: The data would be sorted follow Little Endian when

checked.

**Sync Symbol:** Choose which k-code for syncing.

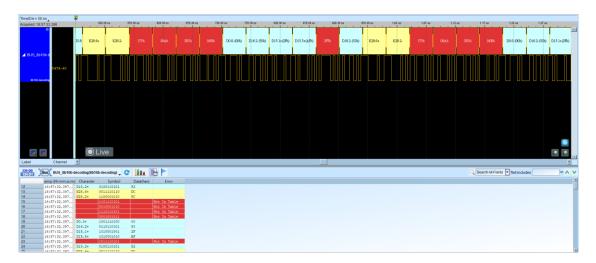

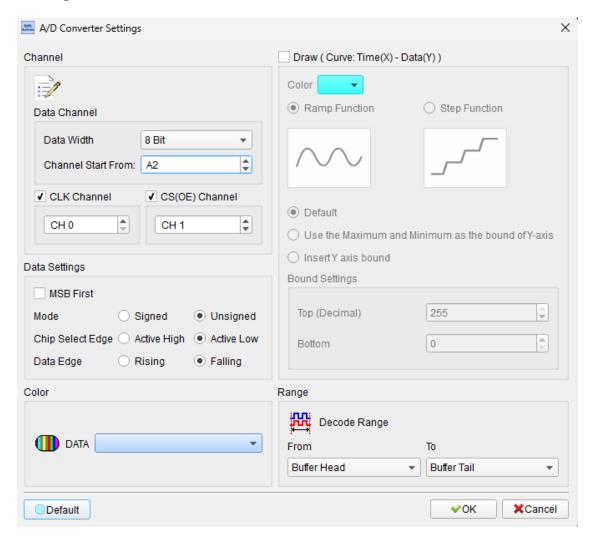

#### A/D Converter

A/D Converter (Analog-To-Digital Converter), is a device that uses sampling to convert a continuous quantity to a discrete time representation in digital form.

# **Settings**

Data Channel Start From: ADC data channel start from

**CLK Channel:** CLK IN channel of ADC, enable CLK channel and Data Edge option when checked.

**CS(OE) Channel:** Chip Select channel of ADC, enable CS channel and Chip Select Edge option when checked.

Data Width: ADC data width, range: 4Bit ~ 32Bit

MSB First: Data bit starts form MSB; LSB defaulted

Chip Select Edge: Set the chip select edge; Active Low defaulted

Data Edge: Set the Data Edge; Falling Edge defaulted

Curve: Time(X)-Data(Y) Show the diagram in form of time as X axis; data as Y

axis.

Ramp/Step Function: Select Ramp/Step curve, Ramp Function defaulted

Color: Select the curve color

# **Bound Value Range:**

**Default:** The maximum value that can be represented using the data width is the upper bound.

**Use the maximum and minimum as the bound of Y axis:** Use the maximum data as the top bound of Y axis and minimum data as the bottom bound of Y axis.

**Insert Y axis bound:** Set the maximum and minimum bounds of Y axis.

### Result

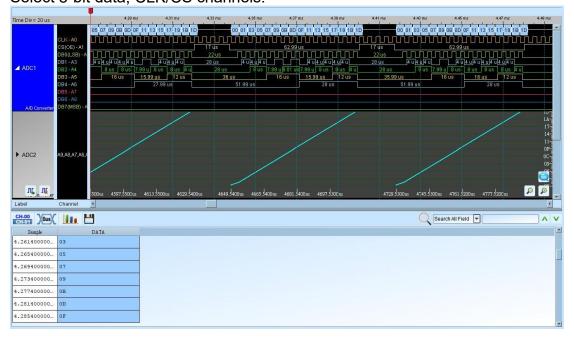

Select 8-bit data, CLK/CS channels:

# Select 8-bit data, CLK:

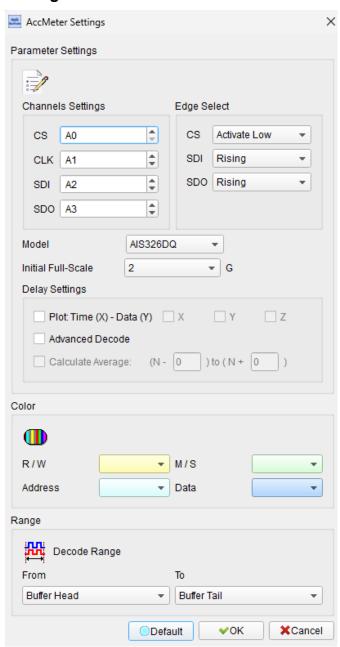

#### **Accelerometer**

Accelerometer (AccMeter) decoder is the SPI interfaced accelerometer data decoder, which provides bus value to acceleration value conversion and curve drawing function.

# **Settings**

# **Channel Setting:**

**CS:** Chip Select, must specified the active state of the CS pin.

**CLK:** Clock

**SDI:** Data Input Pin, must specified the data sampling edge.

**SDO:** Data Output Pin, must specified the data sampling edge.

### **Edge Setting:**

**CS:** Set the trigger edge of Chip Select to High or Low.

**SDI:** Set the trigger edge of SDI to Rising or Falling.

**SDO:** Set the trigger edge of SDO to Rising or Falling.

**Model:** The IC model of the target accelerometer.

Initial Full-Scale: The default Full-Scale setting.

### Display Setting, Enable when checked:

**Plot:** Enable/Disable to display the waveform in Time-Value curve.

**Advanced Decode:** Enable/Disable the address, value convert function.

Calculate Average: Enable/disable the average statistic function, the

statistic range is ±255 data.

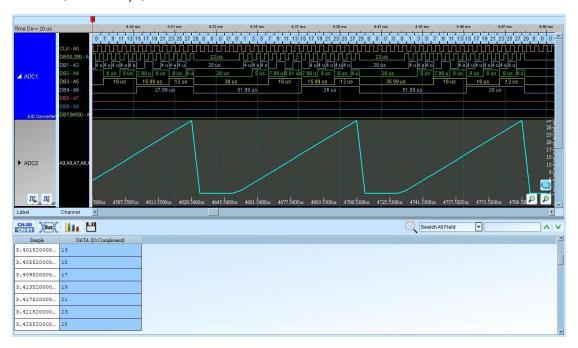

#### Result

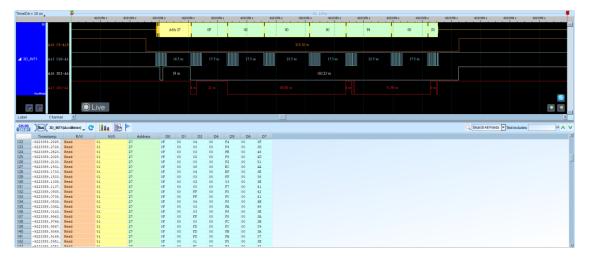

### Standard decoder result

### Advanced decode result + Time-Value curve display

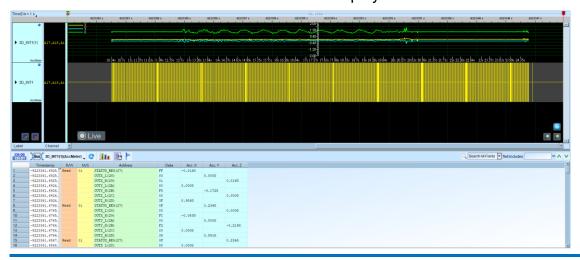

### **AD-Mux Flash**

AD-Mux Flash is one kind of parallel flash that utilize an Address and Data multiplexed interface.

# **Settings**

Amax: Setting the number of address pin.

**Quick Setup/User Defined:** Only set ADQ[0](LSB) when select the Quick Setup, other channels will be set automatically. When check User Defined and press the button will show the dialog below:

Flash: Control pins of flash.

**PSRAM:** Control pins of PSRAM. Some MCP include Flash and PSRAM in one package. It will decode PSRAM at the same time when "has PSRAM" is checked.

**Configuration:** The default setting of configuration register. User must set here to make a correct analysis.

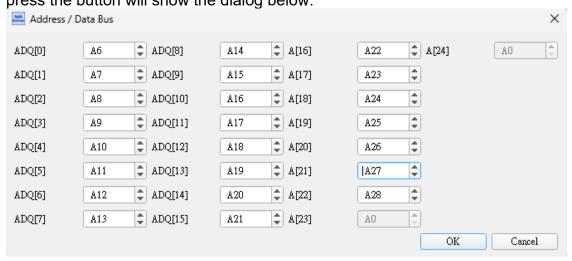

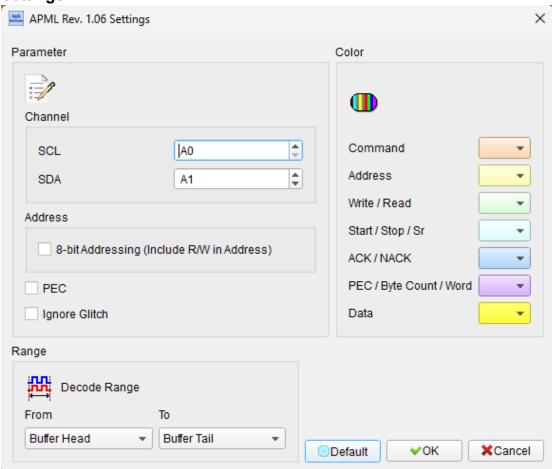

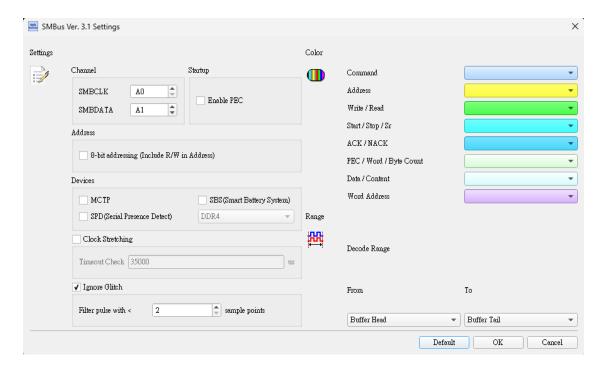

### **APML**

APML protocol is established by AMD for it's Opteron CPU platform.

# **Settings**

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

8-bit addressing (Include R/W in Address): Show 8-bit addressing (include

7-bit addressing and 1-bit R/W). Enable when checked.

**PEC:** Packet Error Check. Enable when checked.

**Ignore glitch:** Ignore the glitch when the slow transitions. Enable when

checked.

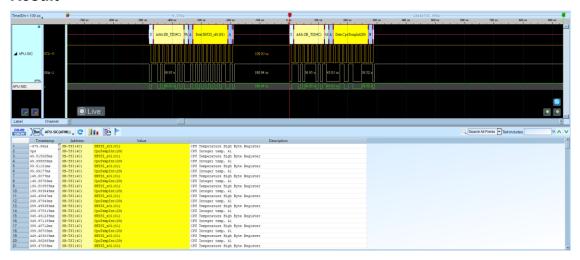

### **AVSBus**

AVS stands for Audio-Visual Coding Standard, which is a video and audio coding standard used to compress, transmit and decode digital video and audio data.

### **Settings**

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

**AVSBus:** Set the decoded data type to SData or MData.

**Detail Report:** Show details in report area, enabled when checked.

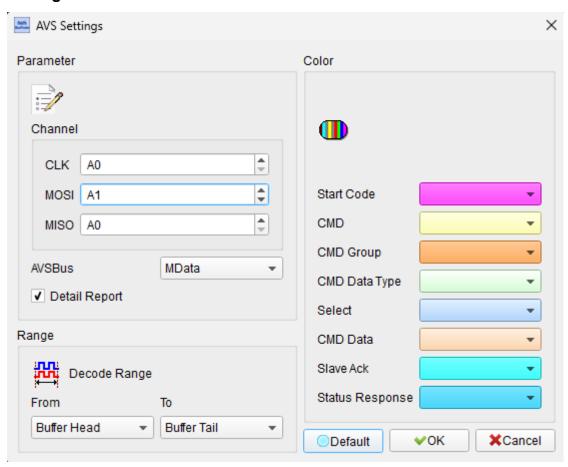

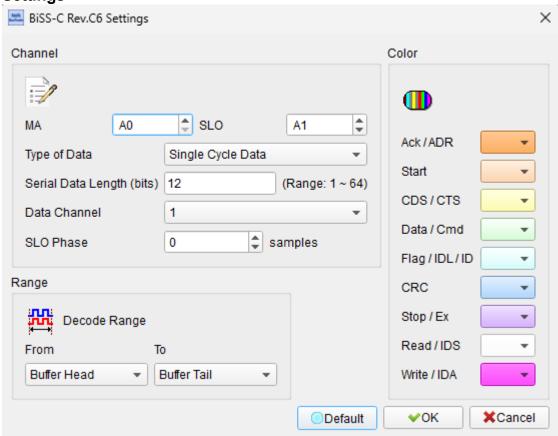

#### **BiSS-C**

BiSS-C (Bidirectional Synchronous Serial C-mode) designed by Ic-Haus. The BiSS Interface is based on a protocol which implements a real time interface. It enables a digital, serial and secure communication between controller, sensor and actuator. It is used in industrial applications which require transfer rates, safety, flexibility and a minimized implementation effort.

#### **Settings**

MA/SLO: Setting the channel of MA and SLO.

**Type of data:** Setting the type you want to decode. It include "Register Data-CDM", "Register Data-CDS", "Single Cycle Data".

**Serial data length(bits):** Setting the data length when Single Cycle Data mode.

**Data Channel:** Startup setting, users need to provide the number of slaves as the base information for decoding.

**SLO Phase:** Sets the delay phase of the SLO.

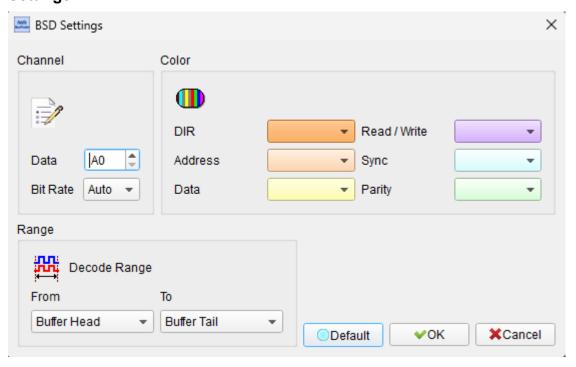

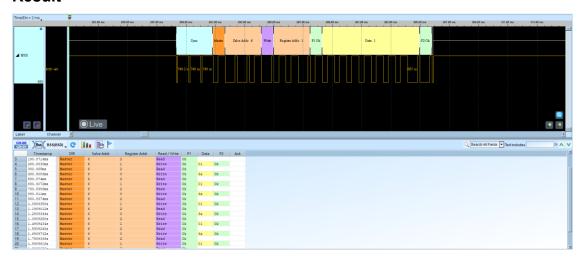

#### **BSD**

BSD(Bit Serial Device) is a serial communications protocol for battery monitoring in automotive application.

# **Settings**

Data: The BSD data.

Bit rate: The bit rate of the BSD data

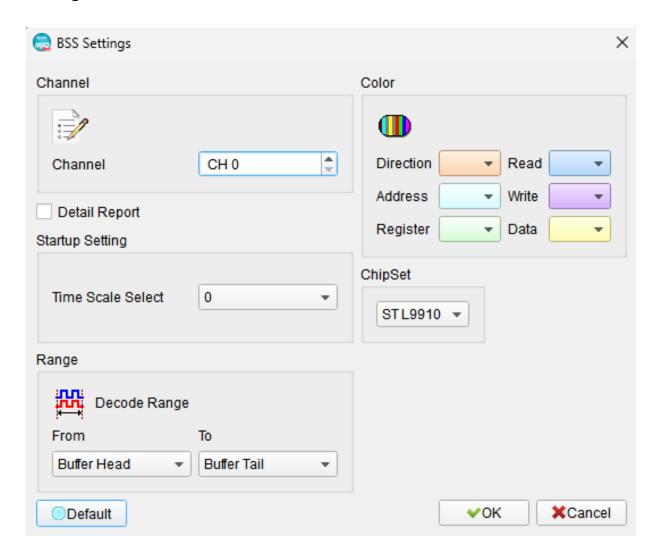

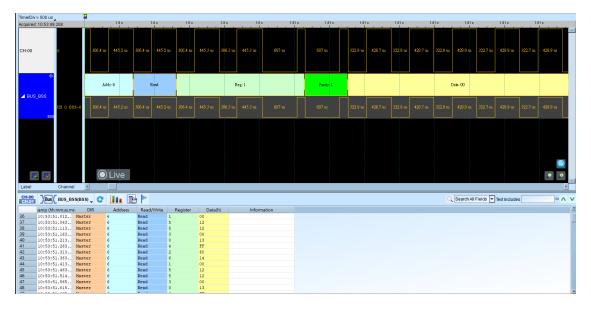

#### **BSS**

Bit Synchronous Single-wire interface (BSS), direct link with the onboard Engine Control Unit (ECU). Aim of the BSS is real time control (through digital protocol) of main electrical parameters, such as voltage regulation and load response timing.

## **Settings**

Channel: Set the signal channel of BSS.

**Detail Report:** Detailed analysis of the byte content. Enable when checked.

**Startup Setting:** Set the value of the Time Scale Select Bit

**ChipSet:** Set the Chipset that are going to be analyzed.

# **Detail Report**

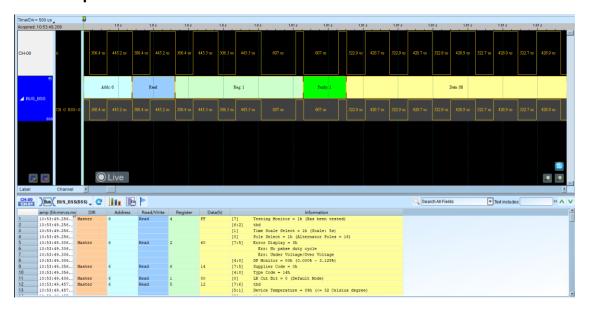

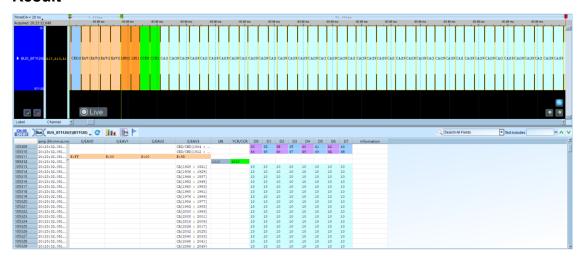

#### BT1120

## Digital interfaces for HDTV studio signals

The BT1120 is used for bit serial port transmission of HDTV signals. It mainly provides image format parameters and data transmission signals for HDTV production and international program exchange, and is backward compatible with old image frequencies of 60, 50, 30, 25 24Hz (progressive, interlaced, frame segmentation), total line number 1125, valid line number 1080 to cover both commercial and developing products. This interface will include all equipment necessary for broadcast and industrial applications.

## **Settings**

**Channel setting:** Set the object to be tested, CLK, each Data 0-7, the channel number connected to the logic analyzer,

Quick Setting: the Data channel setting will be automatically incremented.

Stream: Y, CB/CR stream

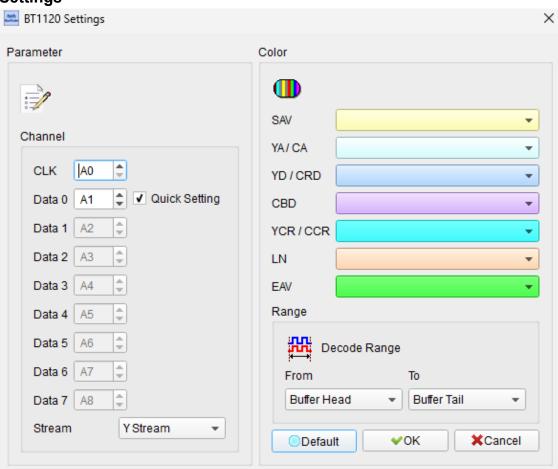

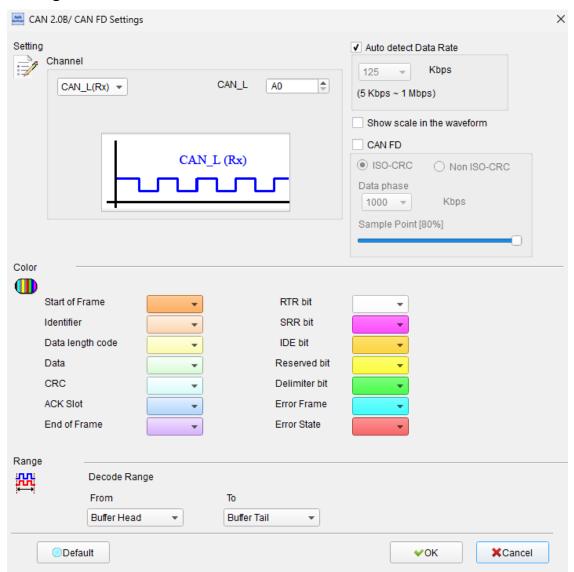

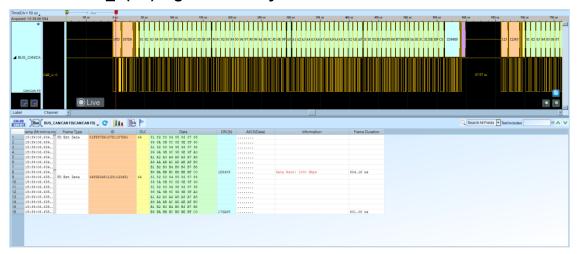

#### CAN 2.0B/ CAN FD

The Controller Area Network (CAN) protocol has version 2.0A (Basic CAN, 11 bits) and version 2.0B (Extended CAN or Peli CAN, 29 bits); both versions have four message types: Data Frame, Remote Frame, Error Frame and Overload Frame as the diagrams below. The CAN Bus has two kinds of data output: CAN High (CAN\_H) and CAN Low (CAN\_L).

The data rate is flexible in CAN FD (CAN with Flexible Data-Rate). When CAN FD is transferring, it is 64 (bytes/per data) and including CRC17/CRC21.

## **Settings**

#### **Channel Settings:**

CAN\_H/CAN\_L(RX): Can directly measure the stabilized physical layer or the

logic signal converted by the transceiver, the best signal to measure is the logic signal Rx.

#### **Auto Detect Data Rate:**

- **I.** When checked, the program assists in calculating the data rate.

- II. When unchecked, user can choose the built-in Data Rate setting or input Data Rate by yourself.

- III. The allowable input data rate range is 5Kbps-1Mbps.

- IV. If CAN FD function is checked, this function will be disabled automatically because the Data Rate will be changed.

**Show Scale in Waveform:** When the box is checked, a scale point is displayed on the top of the waveform, which is convenient to check the bit cutting status. This function is not available if CAN FD is checked.

#### **CAN FD Setting:**

**ISO CRC/Non ISO CRC:** User can adjust the rules of ISO CRC analysis and calculation.

## Data Only:

- I. When checked, this function enables you to set the amount of data to be displayed in the analysis report, which can be set from 8 bytes to 60 bytes, and the data outside the set range will be deleted and not be displayed in the report, which is convenient for you to use when you view the report quickly.

- II. When unchecked, all Data will be displayed.

**Report Format:** Check this box to set the width of the data fields to be displayed in the analysis report, which can be set to 8, 16, or 32 bytes. 8 bytes will be displayed when the box is unchecked, and the following is an example of the application:

Data field width set to 8 bytes.

| Frame Type  | ID               | DLC | Data                    | CRC(h) |

|-------------|------------------|-----|-------------------------|--------|

| FD Ext Data | 01F587D6(07D;187 | 64  | 81 82 83 84 85 86 87 88 |        |

|             |                  |     | 89 8A 8B 8C 8D 8E 8F 90 |        |

|             |                  |     | 91 92 93 94 95 96 97 98 |        |

|             |                  |     | 99 9A 9B 9C 9D 9E 9F A0 |        |

Data field width is set to 16 bytes.

| Frame Type  | ID               | DLC |            |    |    |    |            |    |            | ı         | Data | ı  |    |    |    |    |    |    |

|-------------|------------------|-----|------------|----|----|----|------------|----|------------|-----------|------|----|----|----|----|----|----|----|

| FD Ext Data | 01F587D6(07D;187 | 64  | 81         | 82 | 83 | 84 | 85         | 86 | 87         | 88        | 89   | 8A | 8B | 8C | 8D | 8E | 8F | 90 |

|             |                  |     | 91         | 92 | 93 | 94 | 95         | 96 | 97         | 98        | 99   | 9A | 9в | 9C | 9D | 9E | 9F | A0 |

|             |                  |     | <b>A</b> 1 | A2 | A3 | A4 | <b>A</b> 5 | Α6 | <b>A</b> 7 | <b>A8</b> | Α9   | AA | AB | AC | AD | ΑE | AF | в0 |

# Use the CAN\_L(Rx) signal for analysis.

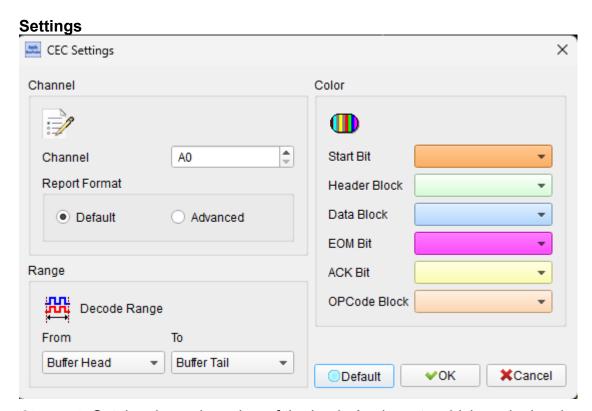

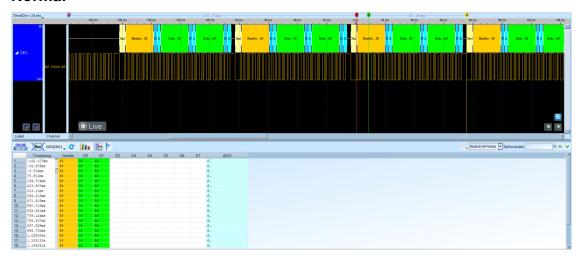

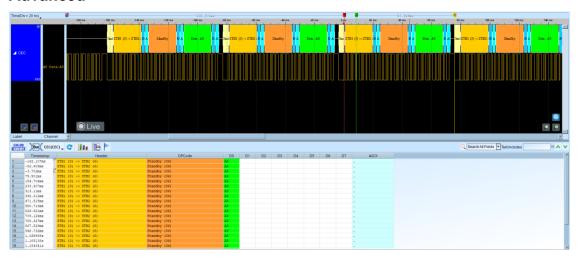

#### **CEC**

Consumer Electronics Control, used for transmitting industrial specification AV Link protocol signals to support a single remote control to operate multiple AV machines, is a single-core, bi-directional serial bus.

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

**Report Format:** There are two types of settings, Advanced and Default. The Advanced mode explains the meaning of the Header and OPCode of the waveform.

# **Normal**

# **Advanced**

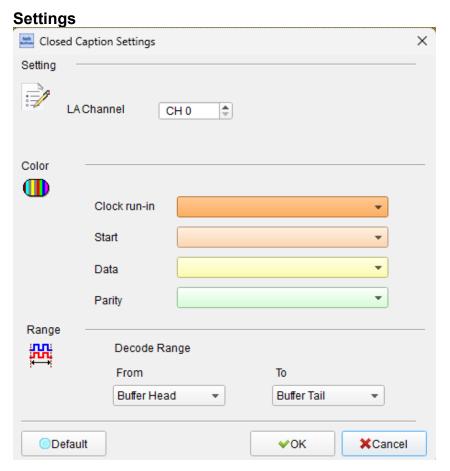

# **Closed Caption**

Closed captioning is the process of displaying text on a TV or video screen. The text is encoded in the video data stream.

LA Channel: Show the selected channel.

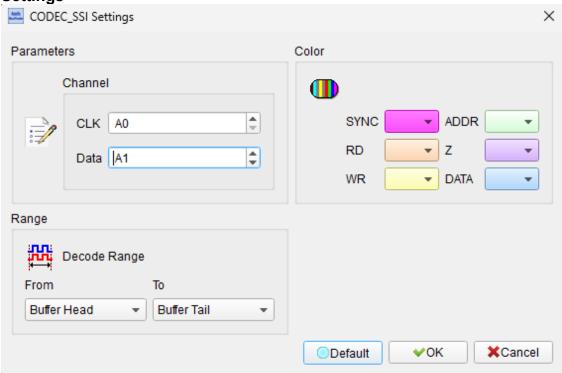

## **Codec SSI**

Serial Synchronous Interface (SSI) signal used by the codec (CODEC) inside the phone

**Settings**

**Channel:** Set the signal on the DUT to the channel number of the logic analyzer.

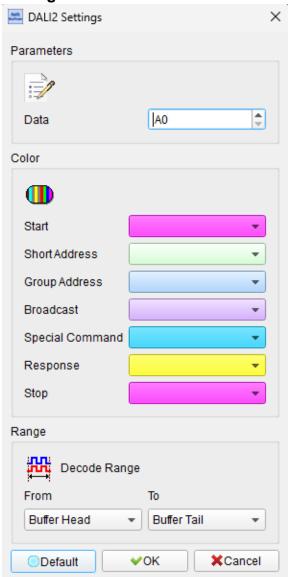

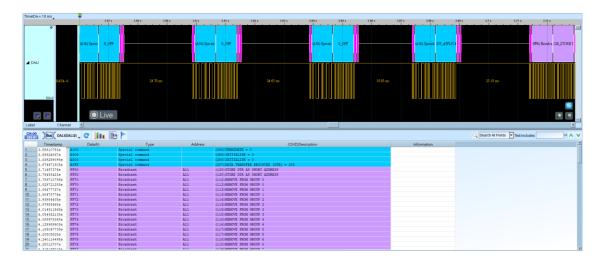

#### **DALI**

Digital Addressable Lighting Interface (DALI) is a technical standard for network-based systems that control lighting in buildings. The DALI standard, which is specified in the IEC 60929 standard for fluorescent lamp ballasts, encompasses the communications protocol and electrical interface for lighting control networks.

# **Settings**

Data Channel: Show the selected channel.

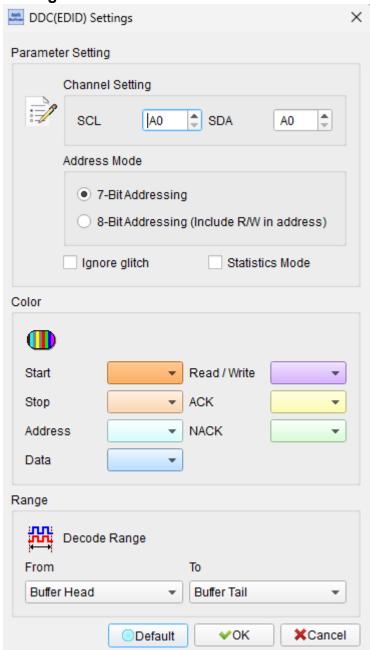

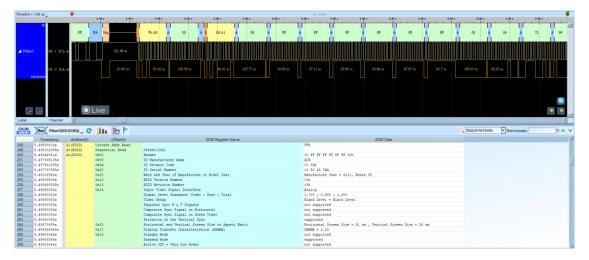

# DDC (EDID)

EDID (Extended Display Identification Data) is I2C protocol base on DDC wire and transmitted monitor information. Now, HDMI, DVI and VGA are support this protocol.

# **Settings**

SCL: CLK of I<sup>2</sup>C. SDA: Data of I<sup>2</sup>C. Address Mode:

7-bit addressing: Show 7-bit addressing

# 8-bit addressing(Include R/W in Address): Show 8-bit

addressing(include 7-bit addressing and 1-bit Rd/Wr).

**Ignore glitch:** Ignore the glitches occurred due to the slow transitions.

**Statistic Mode:** Collect all the data frames into one report by register address order.

#### **DMX512**

DMX512 is a standard for digital communication networks that are commonly used to control stage lighting and effects..

# **Settings** × DMX512 Settings Channel Channel **‡** A0 Data ✓ Auto Detect Baud 250000 Range Decode Range To From Buffer Head Buffer Tail • Default ✓OK **≭**Cancel

Data: Show the selected channel (CH0).

Auto Detect: Set the Baud Rate manually if not selected.

#### Result

Use grayscale to display the decode results.

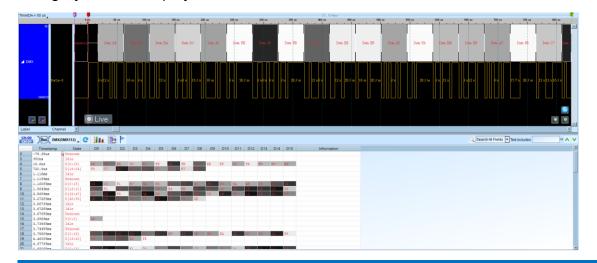

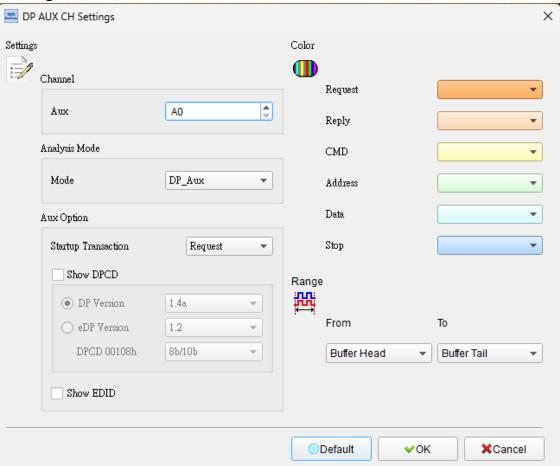

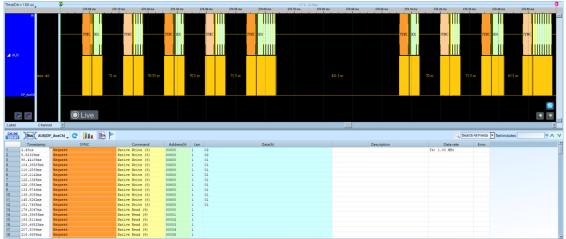

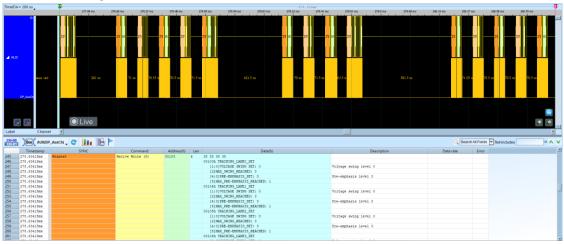

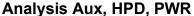

#### **DP Aux Ch**

The DP Aux Ch is to detect the link, configuration and status of the Display Port source. The Display Port is the digital display interface that is specified in the VESA standard. (Support DP 2.1, eDP 1.5)

## **Settings**

Channel: Set the channel to decode

**Show DPCD:** Show the Display Port Configuration data. Enable when checked.

I. DP Version supported to 2.1

II. eDP Version supported to 1.5

III. DPCP 00108h: 8b/10b or 128b/132b encoding options are available.

Mode: Choose the mode DP\_Aux / HPD / PWR

Show EDID: Show the EDID information. Enable when checked.

**Startup transaction:** Set the transaction type of the first frame

Reply Timeout: Set the value of timeout

# Show the DPCD information

## **Accessories:**

https://www.acute.com.tw/en/product/detail143

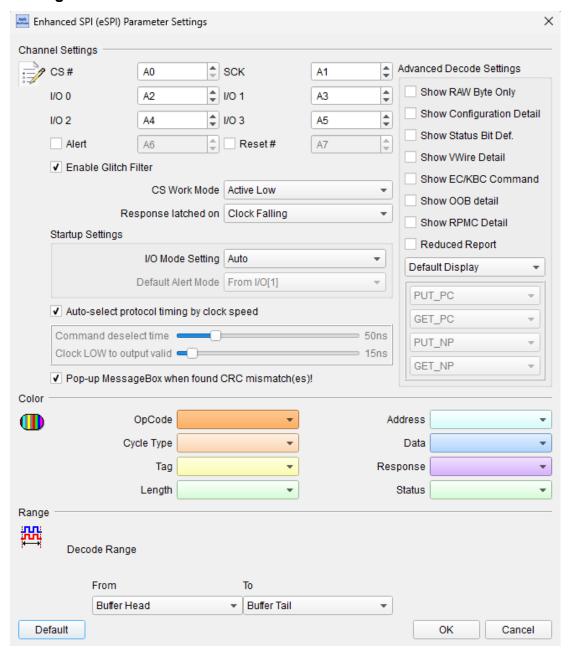

#### eSPI

eSPI is the transmission protocol used in new generation baseboard of Intel, and its specification is to integrate SMBus / LPC / SPI Flash interface to simplify bus and increase transmission efficiency. Source of specification is based on Enhanced Serial Peripheral Interface (eSPI) Interface Base Specification (for Client and Server Platforms) June 2013, Revision 0.75.

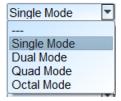

#### **Settings**

#### Channel:

CS#: Chip Select (Active Low)

SCK: Clock

I/O0 – I/O3: Data input / output

Alert: Alert signal (Optional)

Reset: Reset signal (Optional)

# **Startup Settings:**

I/O Mode Setting: Set the initial I / O state to be Single / Dual / Quad, and I /

O state would be switched automatically by the content of the waveform.

Default Alert Mode: Set the channel of Alert signal.

Command deselect time: Set tSHSL, Chip Select# Deassertion Time.

Clock LOW to output valid: Set tCLQV, Output Data Valid Time.

# **Advanced Decode Setting:**

Show Configuration Detail: Show details of SET\_CONFIG / GET\_CONFIG.

Show Status Bit Def.: Show details of Status.

Reduced Report: Reducing the report is easy to check the Command Flow.

Filter Setting: To show or hide the specific OP Code / Cycle Type or

Address range in the report.

Note: The setting of Address Filter would be saved as

LA\eSPI\eSPIFilterX.bin in the work directory.

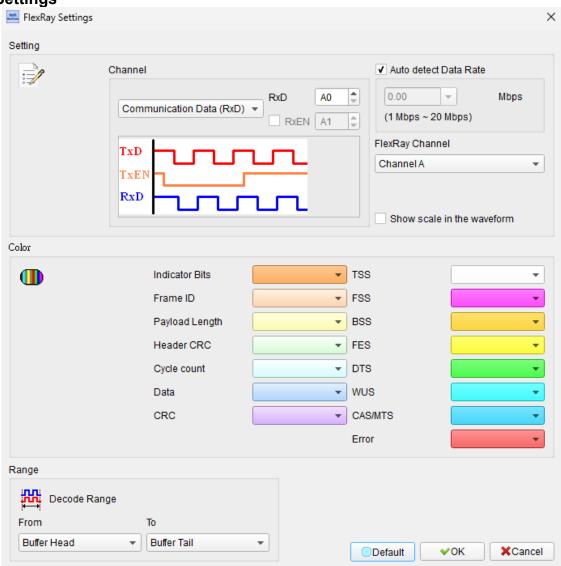

## **FlexRay**

FlexRay is an in-vehicle communication network standard that supports two communication channels, each with a speed of up to 10 Mbps.

**Settings**

Channel: Set the channel, Communication Data (TxD)

**Communication Data (TxD):** The TxD data is from the TxD and TxEN of the FlexRay transceiver.

**Communication Data (RxD):** The RxD data is from the RxD and RxEN of the FlexRay transceiver.

**Auto detect Data Rate:** Default is Auto Bit Rate. If disabled, you may use built-in Bit Rate 10/5/2.5 Mbps or input manually, ranges from 1Mbps-20Mbps.

FlexRay Channel: Channel A or B, for Frame CRC checking.

## **Errors are:**

| Error            | Description                       |  |  |  |  |  |  |

|------------------|-----------------------------------|--|--|--|--|--|--|

| TSS Error        | Unable to detect TSS              |  |  |  |  |  |  |

| FSS Error        | Unable to detect FSS              |  |  |  |  |  |  |

| BSS Error        | Unable to detect BSS              |  |  |  |  |  |  |

| FES Error        | Unable to detect FES              |  |  |  |  |  |  |

| Header CRC Error | The header CRC value is incorrect |  |  |  |  |  |  |

| Frame CRC Error  | The frame CRC value is incorrect  |  |  |  |  |  |  |

# **Abbreviations are:**

| Abbreviation | Description                 |  |  |  |  |  |  |

|--------------|-----------------------------|--|--|--|--|--|--|

| TSS          | Transmission start sequence |  |  |  |  |  |  |

| FSS          | Frame start sequence        |  |  |  |  |  |  |

| BSS          | Byte start sequence         |  |  |  |  |  |  |

| FES          | Frame end sequence          |  |  |  |  |  |  |

| DTS          | Dynamic trailing sequence   |  |  |  |  |  |  |

| CAS          | Collision Avoidance Symbol  |  |  |  |  |  |  |

| MTS          | Media Access Test Symbol    |  |  |  |  |  |  |

| WUP          | Wakeup Pattern              |  |  |  |  |  |  |

| CID          | Channel Idle Delimiter      |  |  |  |  |  |  |

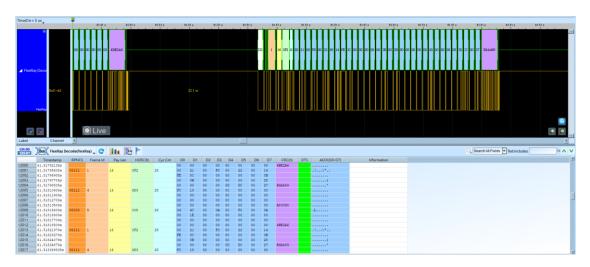

# Result

10Mbps FlexRay Communication Data(RxD)

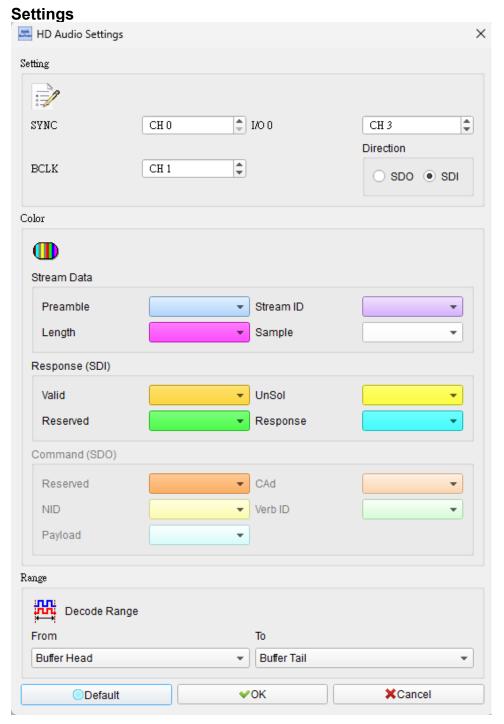

## **HD Audio**

High Definition Audio, also known as HD Audio or by its codename, Azalia, is an audio standard created by Intel to be used on their chipsets, i.e., it is a standard for high-quality on-board audio. In this tutorial we will explain more about this feature.

Channel: Show the selected channel.

**Direction:** Determines whether the I/O data decoding is SDI or SDO; this selection affects the rules of the analysis and causes the color-coded options in the lower field to change.

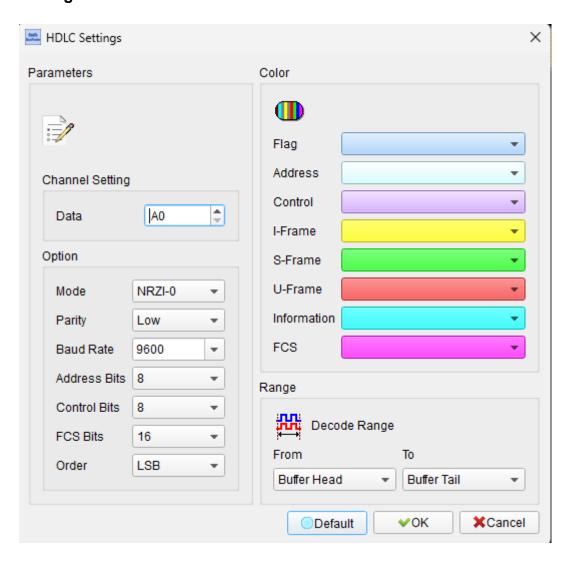

#### **HDLC**

HDLC (High-level Data Link Control) is the default synchronous data link layer protocol used in the equipment of Cisco.

# **Settings**

HDLC: Set the channel of the signal.

Option: Start up Setting of signal analysis

I. Mode: Choose the analysis method.

II. Parity: Set Parity (High / Low)

III. Baud Rate: Set Baud rate

- IV. Address Bits: Set the length of Address Bits.

- V. Control Bits: Set the length of Control Bits.

- VI. FCS Bits: Set the length of FCS (Frame Check Sequence) Bits.

- VII. Order: Bit order of transmission.

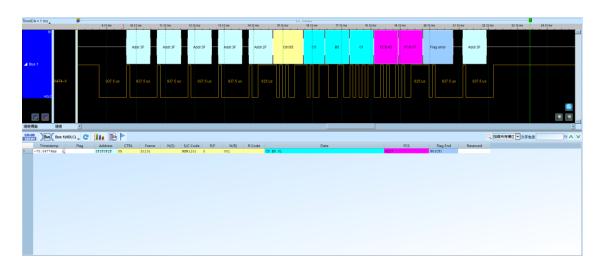

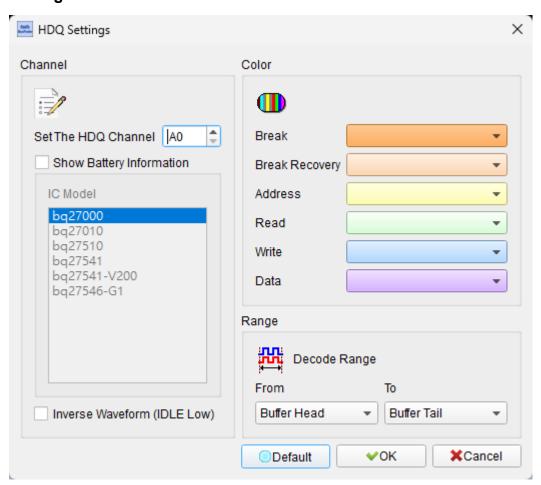

#### **HDQ**

Developed by TEXAS INSTRUMENTS for battery management display applications, primarily in consumer electronics, HDQ is available in two data width formats, 8-bit and 16-bit, with a fixed 7-bit address. An HDQ packet mainly consists of Break, 7 bits Address, 1 bit R/W and 8 bits Data or 16 bits Data. The transmission method is LSB (Least-significant bit) to MSB (Most-significant bit), and the maximum transmission rate is 5 Kbit/s. The maximum transmission rate is 5Kbit/s.

## **Settings**

Channel: Set the HDQ channel: Show the selected channel (CH 0).

**Show Battery Information:** monitor the command between battery and IC.

Invese Waveform (IDLE Low): Invert the waveform. Enabled when

## checked.

## Result

Write: Indicates that the data is written and followed by the data.

Read: Read Indicates that the data is read, followed by the data.

# Show the battery information

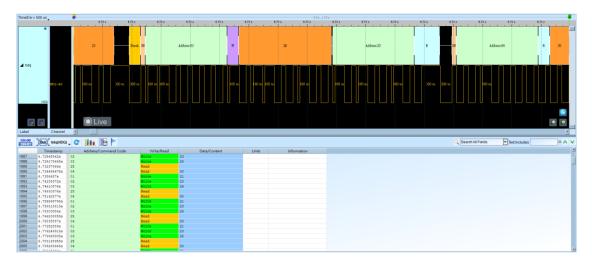

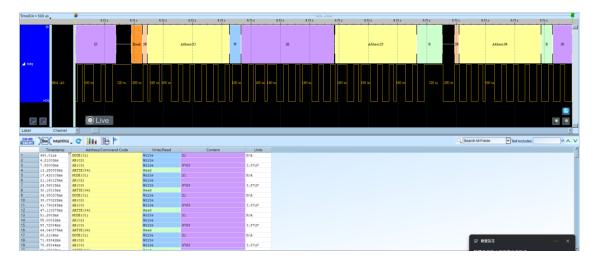

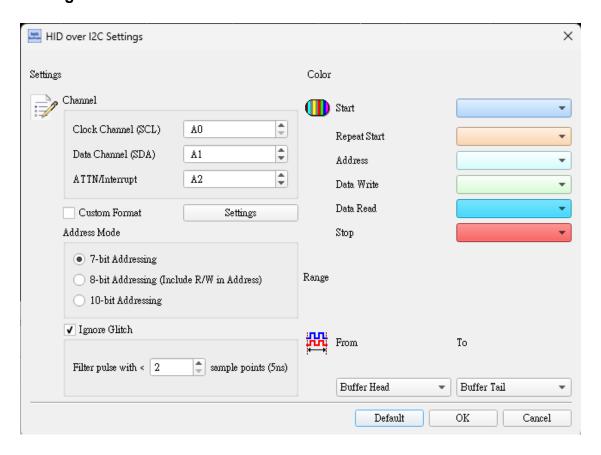

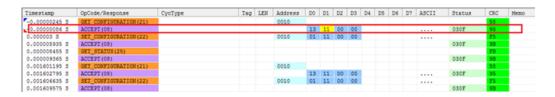

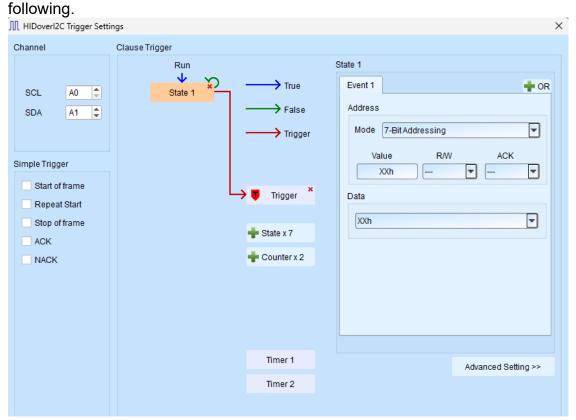

#### HID Over I2C

HID Over I2C (Human Interface Device Over I2C) is mainly used in Windows 8, ARM platform architecture; the other is HID Over USB is used in x86 system, in Windows 8 common support for HID Over I2C bus protocol device is touch pad.

## **Settings**

Channel: Show the selected channels (SCL:CH0, SDA:CH1, ATTN:CH2).

**Custom Format**: Customizable partial analysis content.

**Setting:** Click on it to bring up Notepad to edit the decoding format, the format is as follows: CMD, {Name of parse field 1, Number of bytes in parse field 1, Arrangement of parse field 1}, .....

**7-bit addressing:** Show 7-bit addressing.

**8-bit addressing (Include R/W in Address):** Show 8-bit addressing (include 7-bit addressing and 1-bit Rd/Wr).

10-bit addressing: show 10-bit addressing.

**Ignore glitch:** Ignore the glitches occurred due to the slow transitions. Enabled when checked.

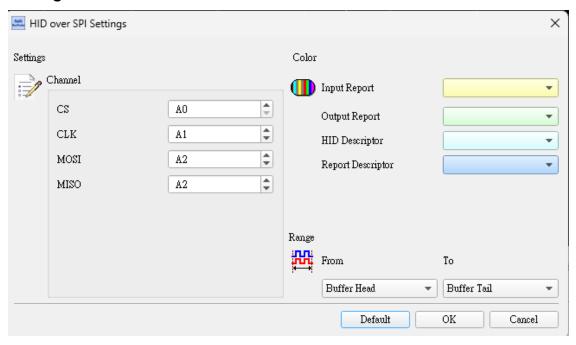

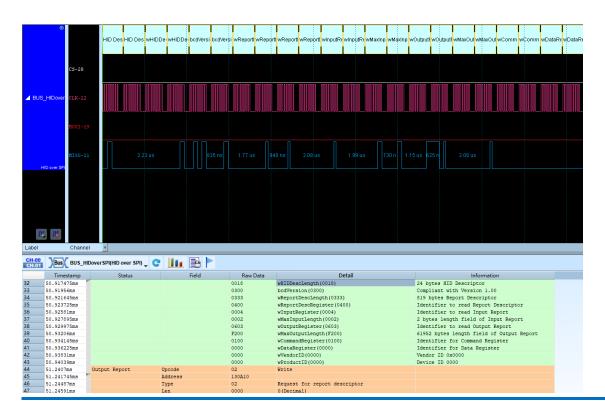

#### **HID Over SPI**

HID Over SPI (Human Interface Device Over SPI) protocol is established by Microsoft. It's applied for Windows 8 ARM platform.

# **Settings**

Channel: Show the selected channels (CS, CLK, MOSI, MISO).

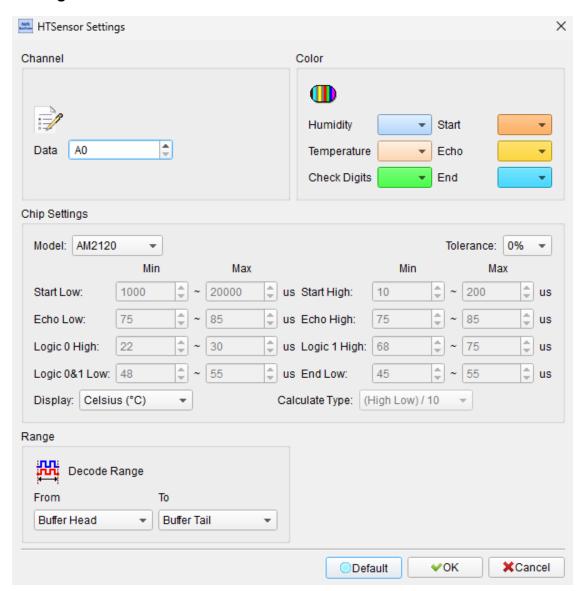

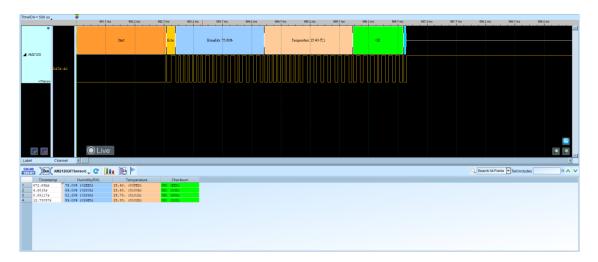

#### **HTSensor**

An HTSensor is a sensor designed to measure and monitor environmental conditions. It typically measures environment-related parameters such as temperature and humidity and provides the corresponding data to a system or device for processing or control. These sensors are widely used in a variety of devices and systems, such as smart homes, automation systems, climate control systems, medical devices, and so on.

## Setting

Data: Set the channel number of the Logic Analyzer to which each signal end is

connected on the object to be tested.

**Chip Setting:** Configure supported chip models or user-defined chip parameter details.

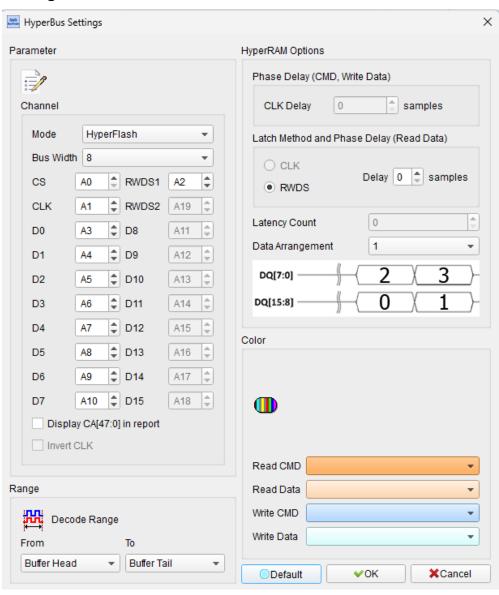

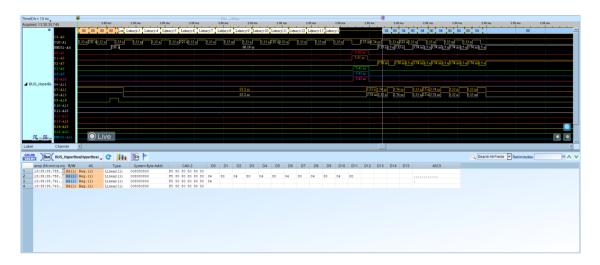

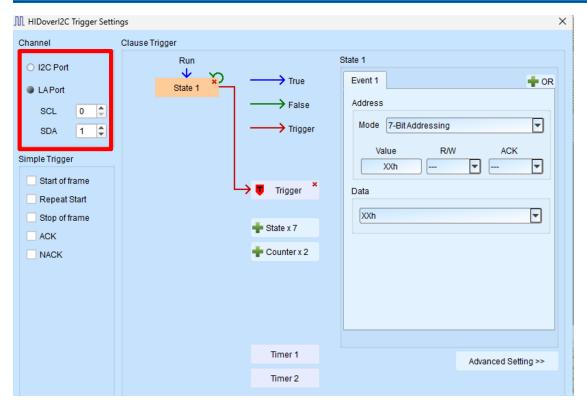

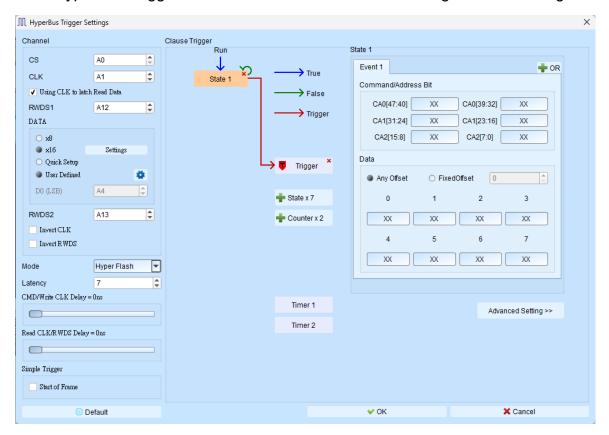

### **HyperBus**

HyperBus is a high-performance memory interface technology designed to increase data transfer rates, especially in embedded systems such as smartphones, tablets, and IoT devices. Proposed by Micron Technology and adopted by several device manufacturers, HyperBus technology can support many different types of memory, most commonly used for connecting Flash memory and DRAM (Dynamic Random Access Memory), while providing faster data read and write speeds than traditional SPI and parallel memory interfaces.

**Mode:** Switching mode, can be set to Hyper Flash or Hyper Ram.

**Bus Width:** Setting the bus width, can be set to 8 or 16.

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

**Display CA[47:0] in report:** Displays CA[47:0] total 48bit information in the report. Available only when the mode is switched to HyperFlash. Enabled when checked.

**Invert CLK**: Invert CLK: Available only when mode is switched to HyperRam. Enabled when checked.

### **HyperRAM Options:**

- Phase Delay (CMD, Write Data): Sets the number of sample points for Delay, valid only when the mode is switched to HyperRam.

- II. Latch Method and Phase Delay (Read Data): Set the number of sample points for CLK (valid only when mode is switched to HyperRam) or RWDS Delay.

- III. Latency Count: Sets the number of Delay CLKs, valid only when the mode is switched to HyperRam.

- IV. Data Arrangement: Sets the mode of the Data Arrangement to one of two modes.

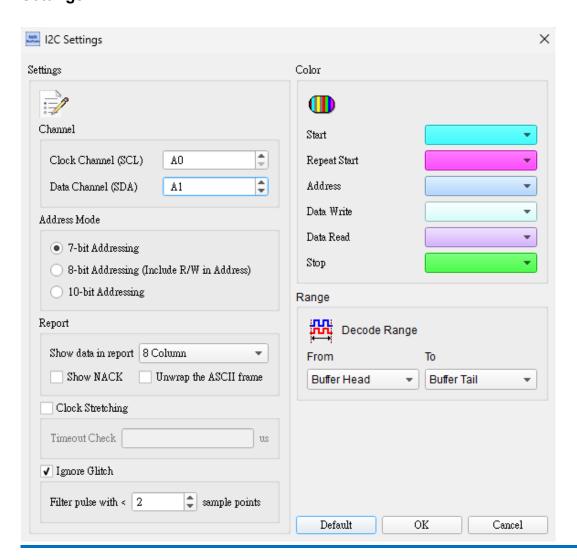

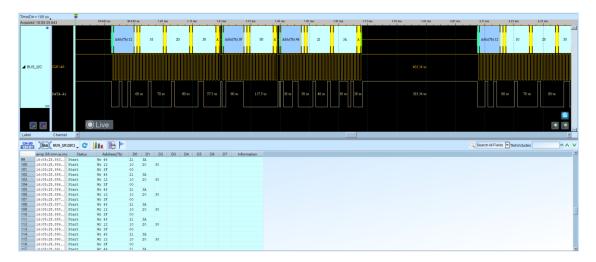

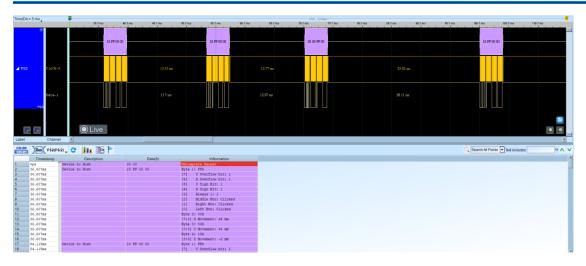

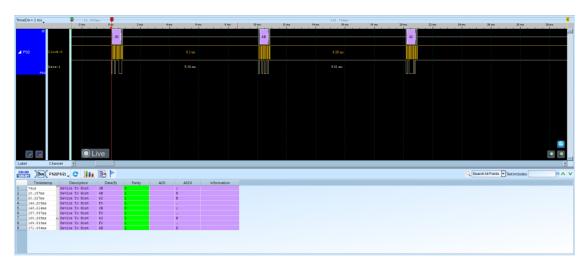

#### I<sup>2</sup>C

I2C is a two-wire serial communications bus, using a multi-slave architecture, developed by Philips in the 1980s to enable motherboards, embedded systems, or cell phones to connect to low-speed peripheral devices, and is a commonly used type of electronic circuit system. I2C uses only two bi-directional signal lines, one clock line (SCL) and one data line (SDA). Signal content has a total of start (Start), address (Address), data (Data), read/write (Read/Write), etc., the transmission method is bidirectional, the data format is divided into two kinds of 8 bits and 10 bits. The transmission rate is 100kbit/s-3.4Mbit/s. The data format is divided into 8 bits and 10 bits.

Clock Channel (SCL): Transfer clock of I<sup>2</sup>C.

**Data Channel (SDA):** Transfer data of I<sup>2</sup>C.

### **Address Mode:**

- 7-bit addressing: Displays the address in 7-bit width and Rd/Wr in

1-bit width.

- II. 8-bit addressing(Include R/W in Address): Displays an 8-bit width address (7-bit width address plus 1-bit Rd/Wr).

- III. 10-bit addressing: Displays a 10-bit width address.

### Report:

- Show data in report: Displays the data in the report area with a choice of 8 or 16 fields.

- II. Show NACK: Marks the Byte as NACK in the field. enabled when checked.

- III. Unwrap the ASCII frame: Add "ASCII" field in the report area.

Enabled when checked.

**Clock Stretching:** Set the length of time for Clock Streching. Enabled when checked.

**Ignore Glitch:** Ignore glitch caused by slow transitions when analyzing. Enabled when checked.

## Result

Wr: Indicates that the data is written.

Rd: Indicates reading data.

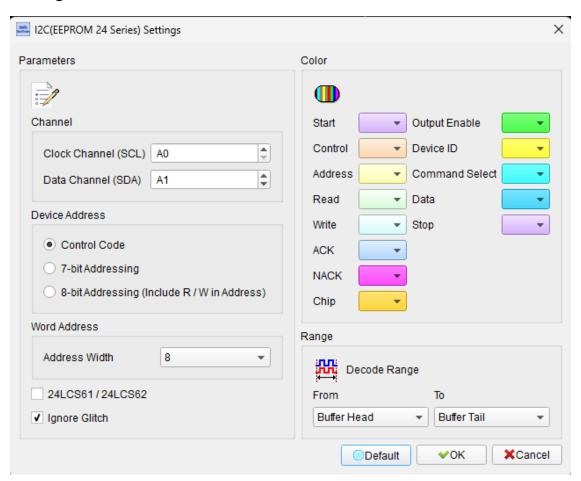

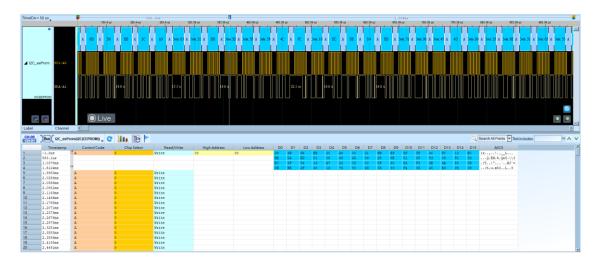

### I<sup>2</sup>C EEPROM

EEPROM, or E<sup>2</sup>PROM, is known as Electrically-Erasable Programmable Read-Only Memory, and the interface of EEPROM components can be classified into serial and parallel, with I<sup>2</sup>C EEPROM belonging to the 2-wire serial EEPROM, and its model is a series starting with 24. I<sup>2</sup>C EEPROM belongs to the 2-wire serial EEPROM, and its model number is a series starting with 24.

## **Settings**

Clock Channel (SCL): Transfer clock of I<sup>2</sup>C.

Data Channel (SDA): Transfer data of I<sup>2</sup>C.

**Device Address:**

- 1. Control Code: Display Control Code.

- IV. 7-bit Addressing: Displays the address in 7-bit width and Rd/Wr in1-bit width.

- 8-bit Addressing (Include R/W in Address): Displays an 8-bit width address (7-bit width address plus 1-bit Rd/Wr).

**Word Address:** Set the number of valid bits of I2C EEPROM address, the default value is 8.

**24LCS61 / 24LCS62:** Select whether to analyze 24LCS61 / 24LCS62. enabled when checked.

**Ignore Glitch:** Ignore glitch caused by slow transitions when analyzing. Enabled when checked.

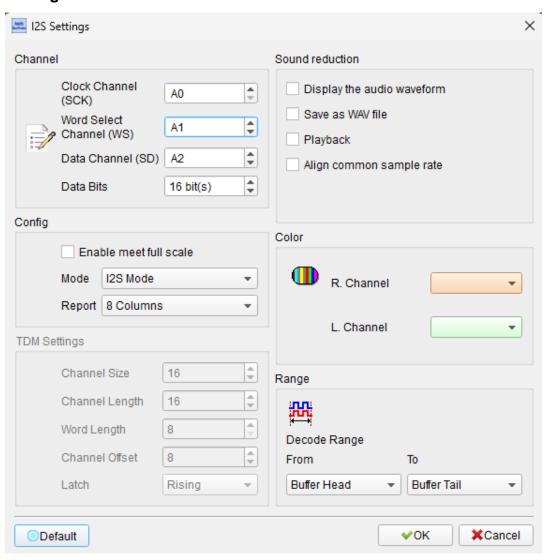

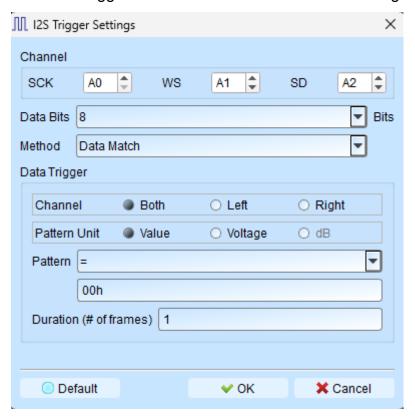

#### I<sup>2</sup>S

I<sup>2</sup>S is an interface standard for transferring digital audio data between ICs. It is a bus standard developed by Philips for transferring audio data between digital audio devices, and is often used for transferring PCM audio from a CD to a DAC in a CD player. The I<sup>2</sup>S standard specifies the hardware interface specifications and the format of the digital audio data, and uses a sequential approach to transmit two groups (left and right channels) of data. It consists of three transmission lines, a clock line (SCK), a word selection line (WS), and a data line (SD). The data format is up to 32 bits.

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

**Data Bits:** The number of bits of analyzed data ranges from 1 to 32 Bits; the default value is 16 Bits.

#### Sound reduction:

- Display the audio waveform: User can draw the waveform of the sound in the Waveform area. Enabled when checked.

- Save as WAV file: All Data can be saved as a sound file (.WAV) and saved in the working directory. Enabled when checked.

- 3. Playback: The default setting is off. This function collects all the data and plays it back after analyzing it. This is the fastest way to confirm that the sound is being transmitted correctly without having to go through the data one by one. Since the length of playback time depends on the depth of data that the Logic Analyzer can record, it is recommended that you increase the Logic Analyzer's data depth and reduce the number of channels used by the Logic Analyzer. Enabled when checked.

- 4. Align common sample rate: Automatically archives the sound waveforms with the sampling rate closest to the commonly used ones (44.1KHz, 48KHz ......). Enabled when checked.

# Config:

- 1. Mode: switch mode base on the needs.

- i. I<sup>2</sup>S Justified

- ii. MSB Justified

- iii. LSB Justified

- iv. PCM

- v. TDM

- Enable meet full scale: Auto-completes missing bits in multiples of 8,

e.g., 15 bits to 16 bits, 17 bits to 24 bits, enabled when checked.

- 3. **Report:** User can select the number of columns displayed in the report area.

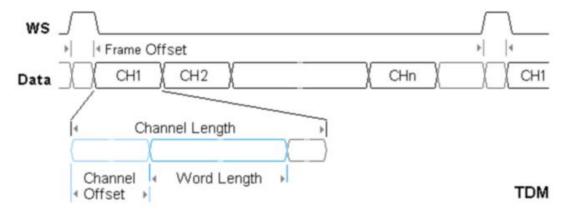

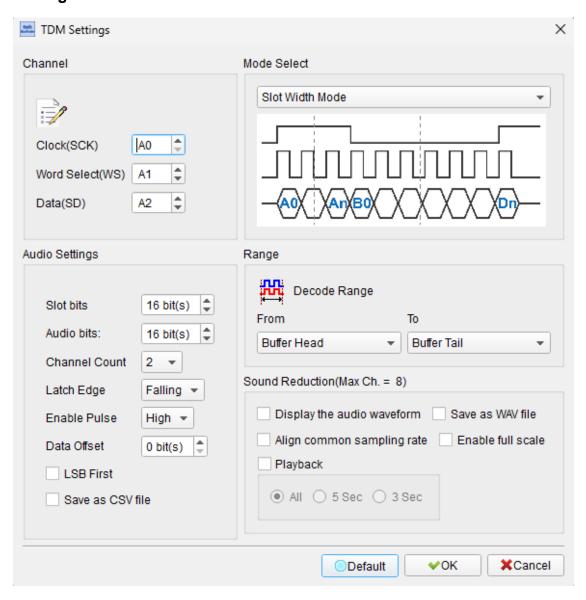

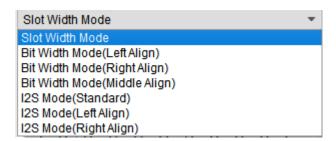

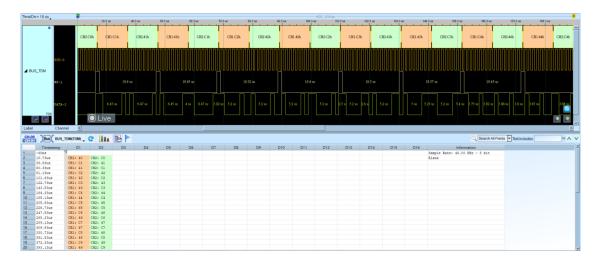

# **TDM Setting Parameter Definitions:**

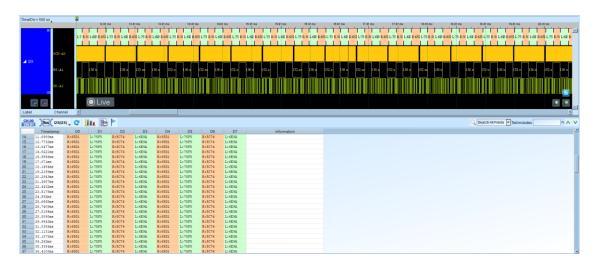

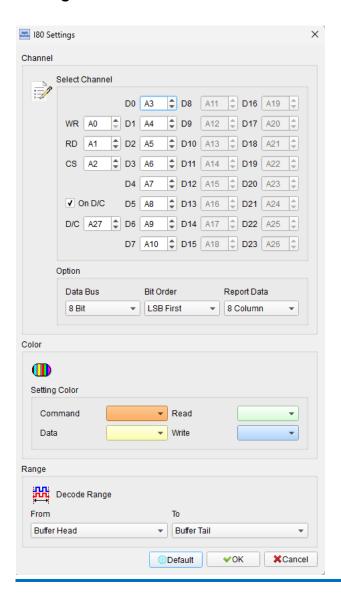

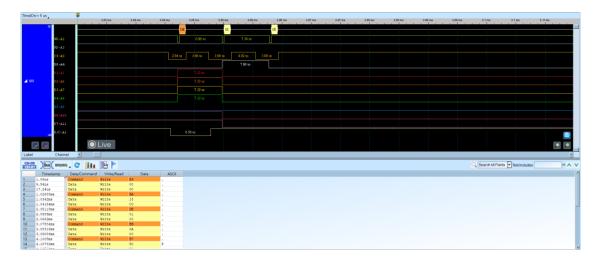

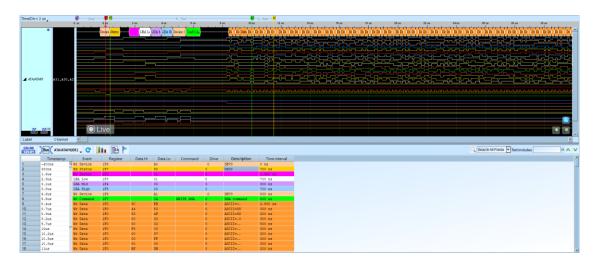

### 180

The Inter 8080-series interface is mainly used for LCM data transfer. It is simply called I80 interface. To analyze the 8080-series, 3 or 4 Ctrl Buses (WR, RD, CS, and D/C) are required, and the Data Bus requires at least 4 bits depending on the user's definition, so at least 7 channels are required: WR, RD, CS, D0-D3, and 8 channels if there is a D/C Pin. The channel numbers of these signals can be adjusted. The channel numbers of these signals can be adjusted. The 8 bits Data bus requires 11 signals: WR, RD, CS, D0-D7, and so on... WR to CH0, and so on.

Select Channel: Show the selected channels (WR, RD, CS, D0, D1, D2, D3,

D4, D5, D6,...).

On D/C: Use the D/C pin as Command (Low) or Data (High).

Data Bus: Select 4 Bit, 8 Bit, 12 Bit, 16 Bit, 20 Bit, or 24 Bit.

Bit Order: Select LSB First or MSB First.

Report Data: Select 8 columns or 16 columns.

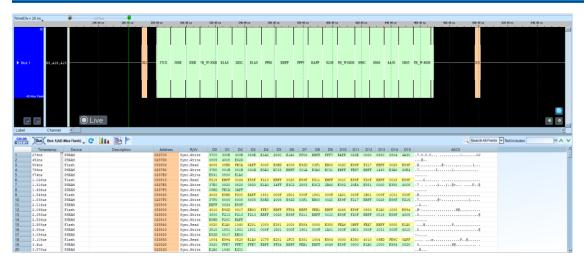

#### IDE

IDE (Integrated Device Electronics) is a standard interface for hard disks, solid-state drives, CD-ROMs, etc. IDE was first used by Western Digital in the U.S. for its hard disk sales business. The name IDE was first used by Western Digital in the United States for their hard disk sales business. The official specification name is ATA/ATAPI (Advanced Technology Attachment/AT Attachment Packet Interface). The ATA specification has continued to be added to due to the increased capacity of hard disks, the need for higher transfer speeds, and the constant evolution of storage devices. In 1998, the ATAPI specification was added to ATA-4, allowing ATA to connect to optical drives and other storage media. In 2003, the SATA (Serial ATA) specification was released, which retroactively renamed the original Parallel ATA to PATA (Parallel ATA) to differentiate it.

To analyze IDE, because it is a parallel transmission, it needs to use more channels, so we have to divide it into three types.

Normal channel (11 pin): Its signals are DASP-, DIOR-:HDMARDY-:HSTROBE, DIOW-:STOP, DMACK-, DMARQ, INTRQ, IORDY:DDMARDY-:DSTROBE, PDIAG-:CBLID-, RESET-, CSEL and IOCS16. -.

Register channel (5 pin): its signals are CS(0:1)- and DA(2:0).

Data channel (16 pin): its signal is DD(15:0).

We recommend that IDE bus of the target system to be connected to the instrument as the following table:

| IDE Pin No. | IDE Pin name | III) E PIN DASCRINTION | LA default Channel<br>No. |

|-------------|--------------|------------------------|---------------------------|

| Pin1        | Reset-       | Hardware reset         | Channel 0                 |

| Pin2        | Ground       |                        |                           |

| Pin3        | DD7          | Device data            | Channel 1                 |

| Pin4        | DD8          | Device data            | Channel 2                 |

| Pin5        | DD6          | Device data            | Channel 3                 |

| Pin6        | DD9          | Device data            | Channel 4                 |

| Pin7  | DD5                            | Device data                                                     | Channel 5  |

|-------|--------------------------------|-----------------------------------------------------------------|------------|

| Pin8  | DD10                           | Device data                                                     | Channel 6  |

| Pin9  | DD4                            | Device data                                                     | Channel 7  |

| Pin10 | DD11                           | Device data                                                     | Channel 8  |

| Pin11 | DD3                            | Device data                                                     | Channel 9  |

| Pin12 | DD12                           | Device data                                                     | Channel 10 |

| Pin13 | DD2                            | Device data                                                     | Channel 11 |

| Pin14 | DD13                           | Device data                                                     | Channel 12 |

| Pin15 | DD1                            | Device data                                                     | Channel 13 |

| Pin16 | DD14                           | Device data                                                     | Channel 14 |

| Pin17 | DD0                            | Device data                                                     | Channel 15 |

| Pin18 | DD15                           | Device data                                                     | Channel 16 |

| Pin19 | Ground                         |                                                                 |            |

| Pin20 | Key pin                        |                                                                 |            |

| Pin21 | DMARQ                          | DMA request                                                     | Channel 17 |

| Pin22 | Ground                         |                                                                 |            |

| Pin23 | DIOW-:STOP                     | Device I/O write: Stop<br>Ultra DMA burst                       | Channel 18 |

| Pin24 | Ground                         |                                                                 |            |

| Pin25 | DIOR-:HDMAR<br>DY-<br>:HSTROBE | Device I/O read: Ultra<br>DMA ready: Ultra DMA<br>data strobe   | Channel 19 |

| Pin26 | Ground                         |                                                                 |            |

| Pin27 | IORDY:DDMAR<br>DY-<br>:DSTROBE | I/O channel ready: Ultra<br>DMA ready: Ultra DMA<br>data strobe | Channel 20 |

| Pin28 | CSEL                           | Cable select                                                    | Channel 21 |

| Pin29 | DMACK-                         | DMA acknowledge                                                 | Channel 22 |

| Pin30 | Ground                         |                                                                 |            |

| Pin31 | INTRQ                          | Device interrupt                                                | Channel 23 |

| Pin32 | Obsolete (see note)            | Device 16-bit I/O in ATA-2                                      | Channel 24 |

| Pin33 | DA1           | Device address                                     | Channel 25 |

|-------|---------------|----------------------------------------------------|------------|

| Pin34 | PDIAG-:CBLID- | Passed diagnostics: Cable assembly type identifier | Channel 26 |

| Pin35 | DA0           | Device address                                     | Channel 27 |

| Pin36 | DA2           | Device address                                     | Channel 28 |

| Pin37 | CS0-          | Chip select                                        | Channel 29 |

| Pin38 | CS1-          | Chip select                                        | Channel 30 |

| Pin39 | DASP-         | Device active, device 1 present                    | Channel 31 |

| Pin40 | Ground        |                                                    |            |

Channel: Set channel number for General, Register, and Data Bus.

**Transferring Mode:** User can specify which specification will be used by the device to be tested so that commands can be interpreted correctly during IDE analysis. If it is not specified correctly, the analysis can be performed.

Analysis Report: User can specify that only those registers are displayed in the Display Report window. For example, if the Data Register is unchecked, data about the data register will not appear in the Report window. In this way, the contents of the data registers are filtered out when viewing the analysis results.

#### **IO-Link**

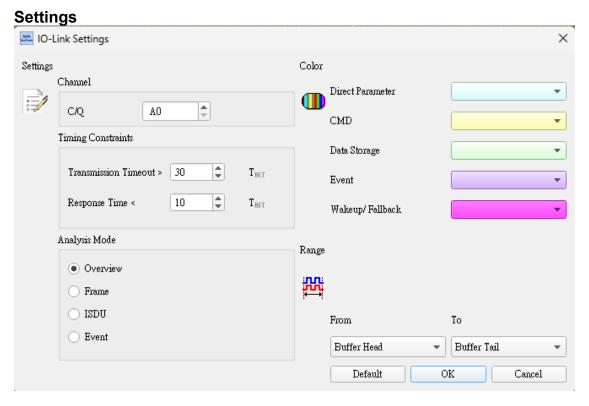

IO-Link is a communication system that connects smart sensors and actuators to automation systems, in accordance with the Single-drop digital communication interface for small sensors and actuators (SDCI) in the IEC 61131-9 standard. This specification includes electrical connections and digital communication protocols through which smart sensors and actuators can interact with automation systems.

**Channel:** Set the C/Q signal terminal on the object under test to be connected to the channel number of the logic analyzer.

### **Timing Constraints:**

- **Transmission Timeout:** The default is 30 TBIT. If IDLE is larger than this value, the next data will be decoded and analyzed by the Master.

- Response Time: The default is 10 TBIT. If IDLE is less than this value and greater than 3 TBIT, the next data will be decoded and analyzed by Device.

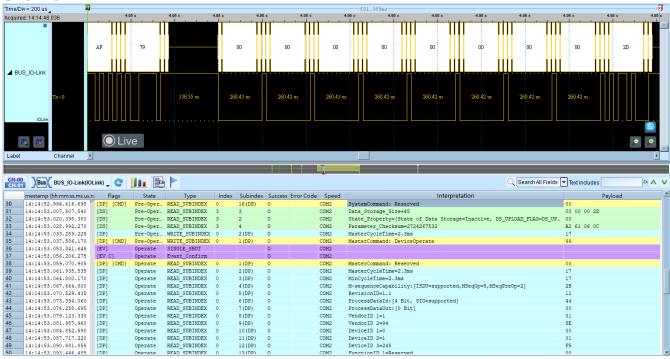

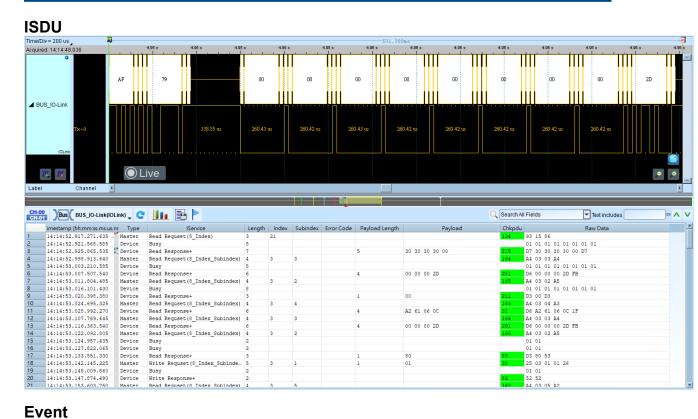

**Analysis Mode:** The report will be analyzed in the selected mode (Overview, Frame, ISDU, Event).

#### Result

#### Overview

#### Frame

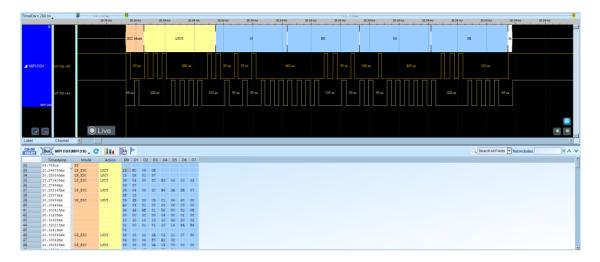

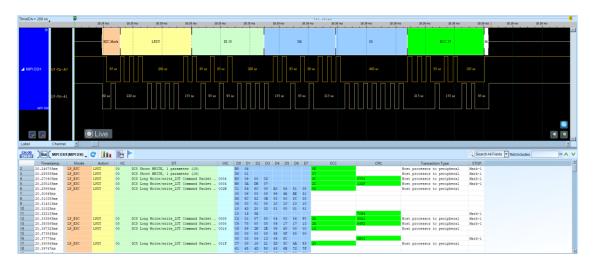

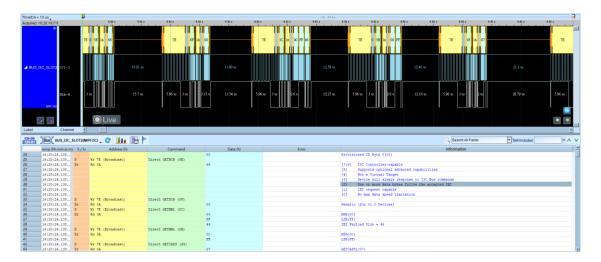

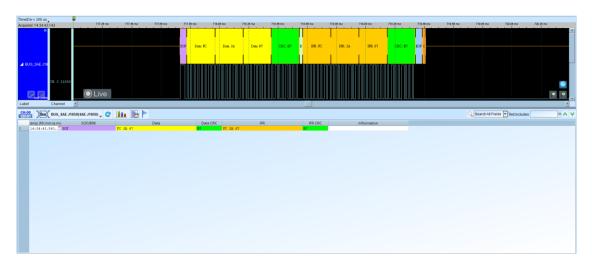

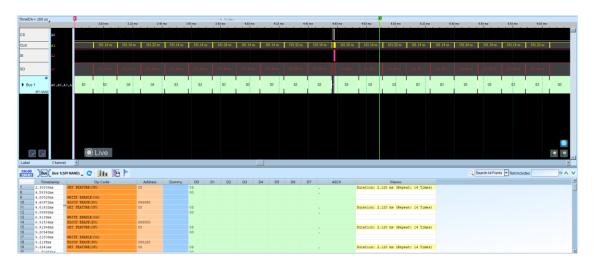

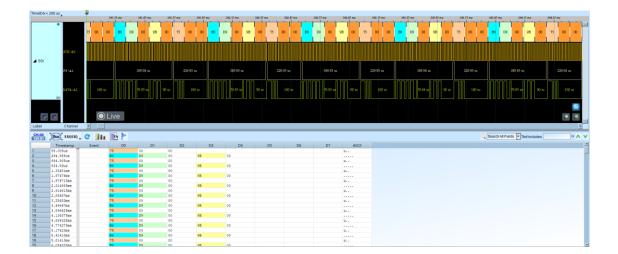

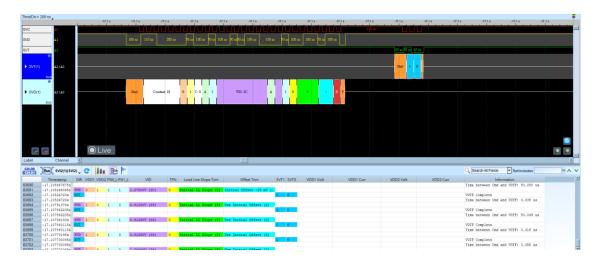

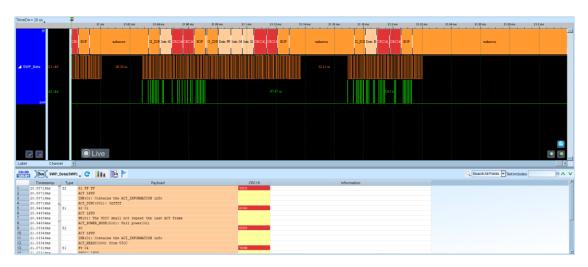

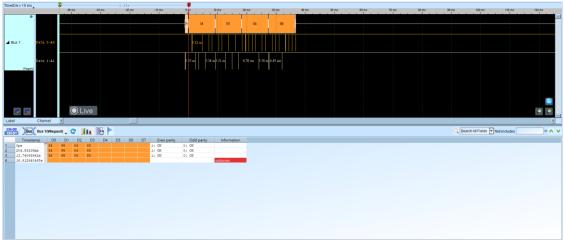

## Time/Div = 200 us \_ Acquired: 14:14:48.036 00 00 00 Live ٥ Q Search All Fields Text includes EX A V Instance Notification SINGLE SHOT Application DEVICE

### **IrDA**

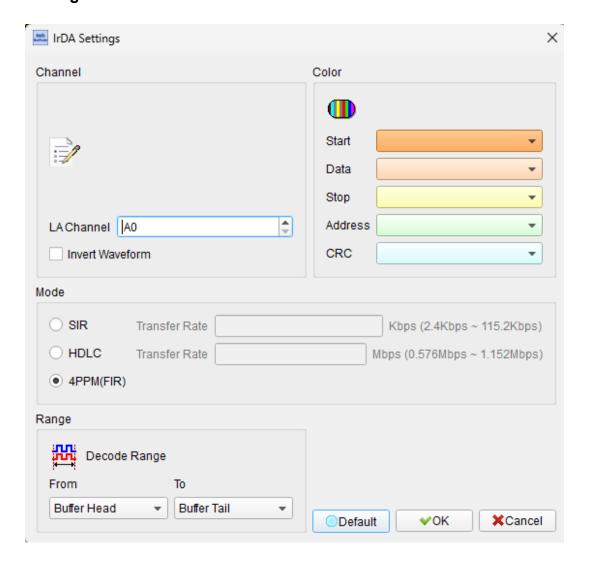

The Infrared Data Association (IrDA) was formed in 1993. The IrDA is point to point user model for a wide range of appliances and devices.

## **Settings**

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

**Invert Waveform:** Invert the waveform before analysis. Enabled when checked.

Mode:

- **1. SIR:** After switching to SIR mode, enter the transfer rate to complete the setting.

- 2. **HDLC:** After switching to HDLC mode, enter the input rate to complete the setting.

- 3. 4PPM (FIR):

### **ISELED**

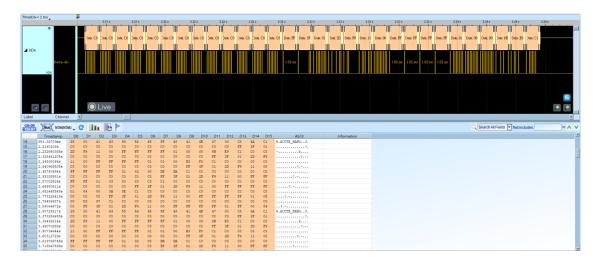

ISELED (Integrated Smart Embedded LED) is a new smart embedded LED technology designed to provide more efficient and intelligent control of LED lighting systems. It combines the luminous performance of LEDs with integrated circuit (IC) technology to enable more precise and flexible control for a wide range of application scenarios, especially in automotive, architectural and consumer electronics.

### **Settings**

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

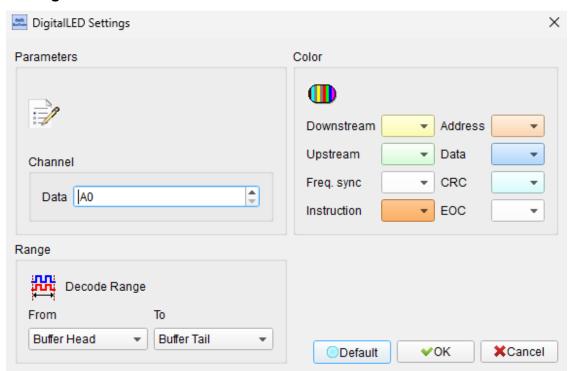

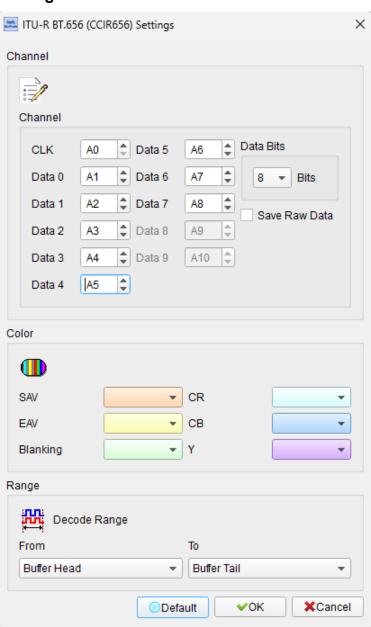

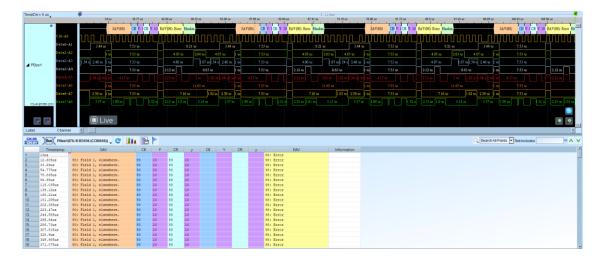

## ITU656 (CCIR656)

ITU656 describes a simple digital video protocol for streaming uncompressed PAL or NTSC Standard Definition TV (525 or 625 lines) signals. The protocol builds upon the 4:2:2 digital video encoding parameters defined in ITU-R Recommendation BT.601, which provides interlaced video data, streaming each field separately, and uses the YCbCr color space and a 13.5 MHz sampling frequency for pixels.

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

Data Bits: Show the number of data bits.

Save Raw Data: Save the result as .bin file. Enabled when checked.

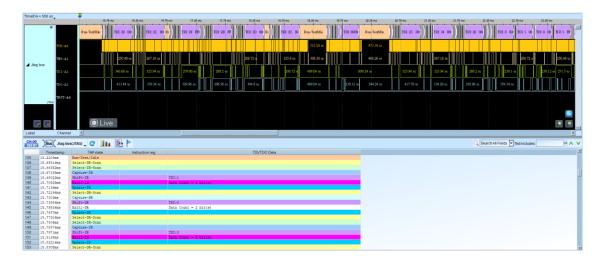

#### **JTAG**

JTAG (Joint Test Action Group) is an international standard test protocol (IEEE 1149.1), mainly used for on-chip internal testing, and nowadays most advanced components support JTAG protocol, such as DSPs, FPGAs, etc. The standard JTAG consists of five signal interfaces: TCK, TMS, TDI, TDO and TRST, four of which are input signal interfaces and the other one is output signal interface. The standard JTAG consists of five signal interfaces: TCK, TMS, TDI, TDO and TRST, four of which are input signal interfaces and the other one is an output signal interface. The basic principle is to define a TAP (Test Access Port) inside the device and test the internal nodes with a dedicated JTAG test tool.

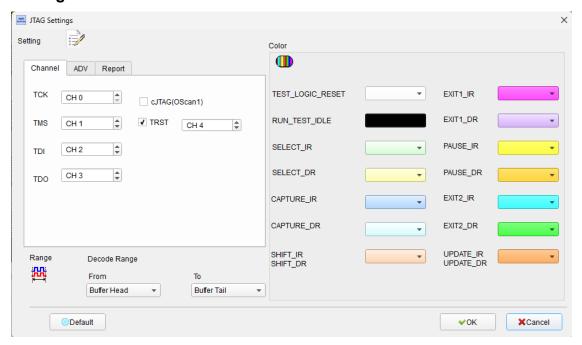

### **Settings**

Channel: Specify the channel number of the Logic Analyzer to be connected with the object to be tested, the TRST pin can be decided by the user, if you are going to use the function of interpreting commands, then the system will decide whether to use the TRST pin or not according to the data of the commands that you have selected, and the user can decide whether to turn on the cJTAG or not, if you turn on the cJTAG option, the TDI/TDO channels are displayed in If

cJTAG is enabled, the TDI/TDO channels will be grayed out, and the TCK/TMS channels will be treated as TCKC/TMSC channels in cJTAG OScan1 mode.

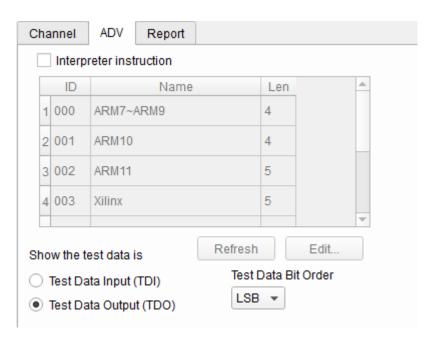

#### Advanced:

- I. Show the test data is: User can select the state of TAP state as Shift-IR, Shift-DR. TDI or TDO data will be displayed in hexadecimal.

- II. **Test Data Bit Order:** The length of data may vary during data transmission by JTAG. Therefore, the user can specify whether the data is LSB First or MSB First when interpreting TDI/TDO.

- III. Interpreter Instruction: If you open the Explain Command function, you will see a list of commands, and the JTAG protocol analyzer will display the commands in the Instruction register during Update-IR.

Users can select "Edit..." function to add and modify the instruction list file (JtagInst.txt) by themselves using the editor. After finishing the modification, click "Refresh" again to update the instruction list.

- IV. Acute Jtag Instruction table(JtagInst.txt): This file is provided by Jtag DLL, users can re-edit this file according to their own needs. We

also supports BSDL format, user can directly add the BSDL file, user can save the time of editing instruction data, please see the last appendix of this unit Acute Jtag Instruction table syntax description.

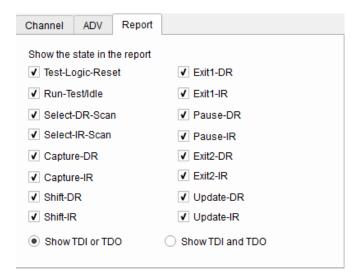

**Report:** To enable report filtering, simply check the items to be displayed in the report window.

I. Show TDI or/and TDO: If choose "Show TDI and TDO", the report area will show the TDI and TDO at the same time.

### **Acute JTAG Instruction table Syntax Description (JtagInst.txt):**

The numbers used in this file are hexadecimal.

##: is comment.

**#ID:** Command list number; the range is 00 - FF and, MUST be entered in order or will be seen as the end of commands.

**#NAME:** Command Name, 32 bytes most will be shown in the command list.

**#LENGTH:** Command length, unit in bits.

#CAPTURE: Command Capture Code, is stored in Instruction Register...

**#INST:** Command List, listed by Command Code and Command Name or will be seen as the end of commands..

**#TRST:** Enter 1 if TREST is needed or enter 0 or nothing if TREST is not needed.

#BSDL: Load the BSDL file. Use the BSDL file as step 1-6.

Example:#ID:00

#NAME:ARM7-ARM9

#LENGTH:4

#CAPTURE:1

#INST:0, EXTEST

#INST:2, SCAN N

#INST:3, SAMPLE/PRELOAD

#INST:4, RESTART

#INST:5, CLAMP

#INST:7, HIGHZ

#INST:9, CLAMPZ

#INST:C, INTEST

#INST:E, IDCODE

#INST:F, BYPASS

#INST:

#ID:01

#BSDL:C:\3256at144\_1532.bsd

## JVC IR

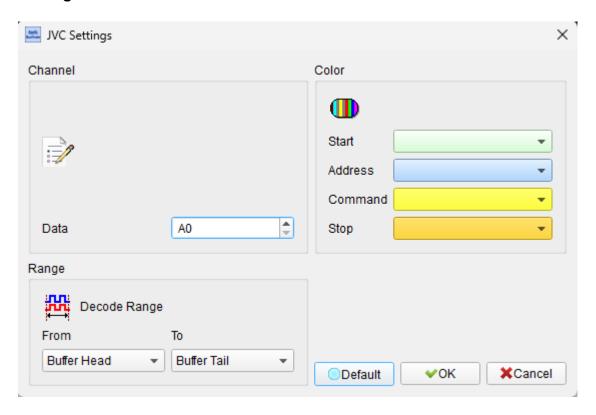

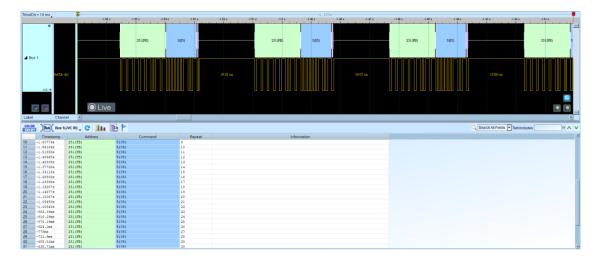

JVC IR refers to products or systems related to infrared (IR) technology introduced by JVC (Japan Victor Company).

# **Settings**

**Channel:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

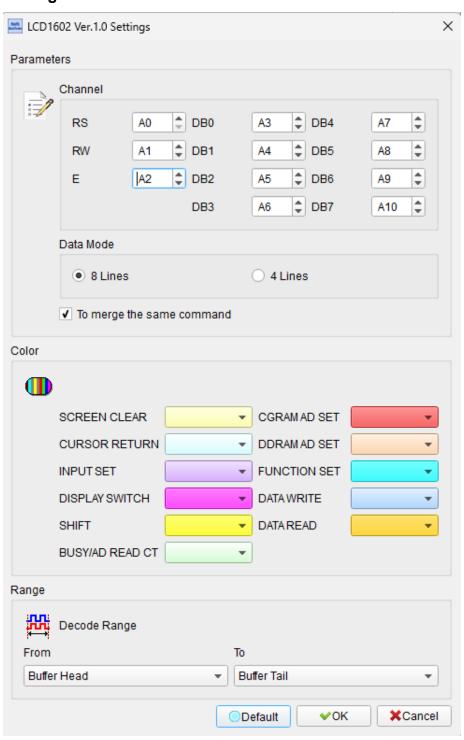

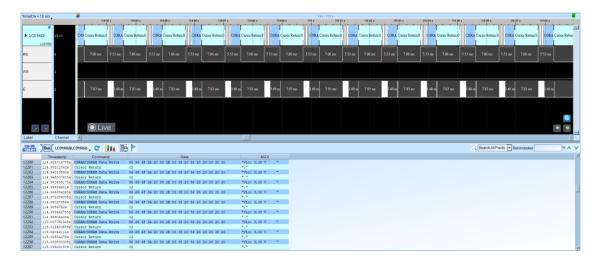

### LCD1602

The Liquid Crystal Display 1602 (LCD1602) bus has 11 data bits:

Instruction/Data Register Select (RS), Read/Write Select (RW), Enable Select

(E) and 8 bits or 4 bits Data Input/Output lines (DB0~DB7/DB0~DB3).

Channel: Show the selected channels (RS: CH0, RW: CH1,..., DB0: CH10).

Data Mode: 8 lines or 4 lines.

To merge the same command: Merge data with its command.

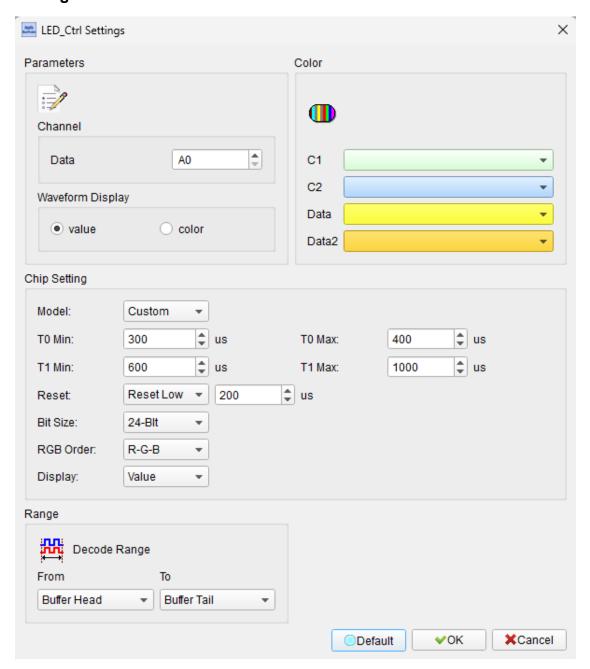

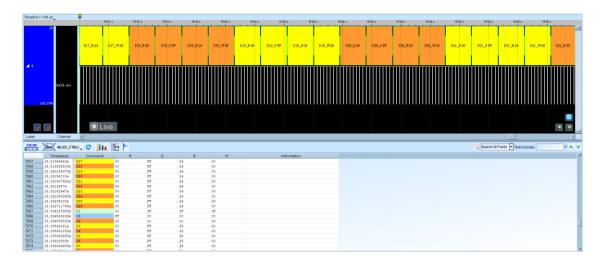

# LED\_Ctrl

LED Controls are made specifically for digital type LEDs. These LEDs contain a special IC chips that allow the user to control each LED or section of LEDs.

## **Settings**

Channel: Show the selected channels.

Waveform display: show value or RGB color in waveform area.

## Chip setting:

Model: User can select the IC model. We now support TM1814 >

WS2811 \ WS2812 \ RT7905 \ HZ0028 and Custom \

# Condition: Idle high

If the time that waveform goes to low between T0 min and T0 max, the bit will decode as zero. If it's between T1 min and T1 max, the bit will decode as one.

**Reset:** if the waveform keeps at high potential over the time, the decoder will reset the start bit.

Bit size: choose 32-bit (WRGB) or 24-bit (RGB).

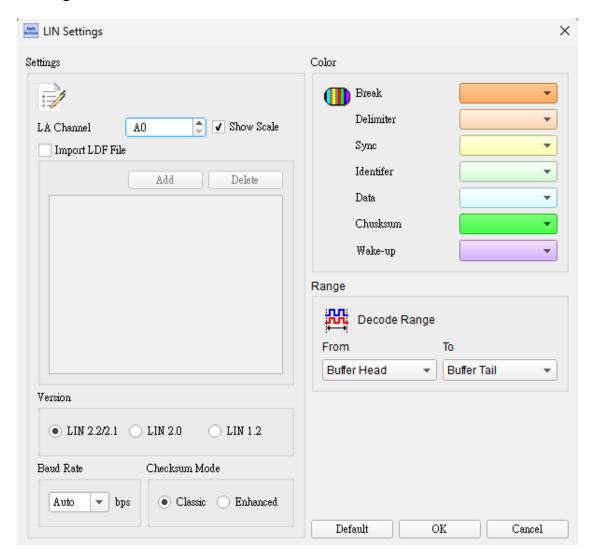

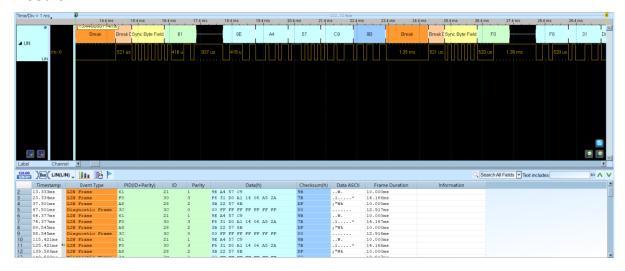

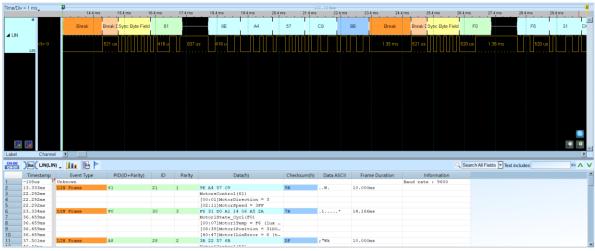

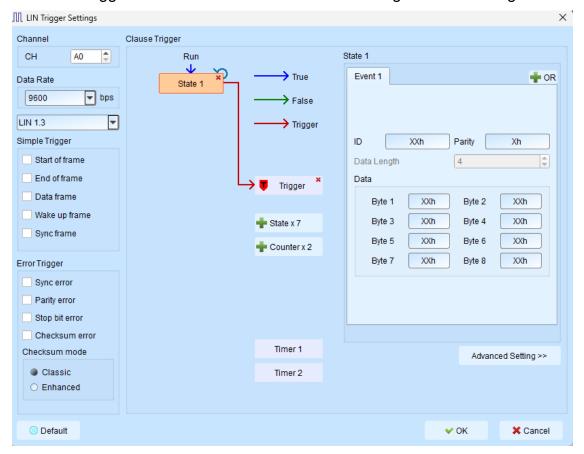

#### LIN

LIN (Local Interconnect Network) is a serial network protocol used for communication between components in vehicles. LIN may be used also over the vehicle's battery power-line with a special LIN over DC powerline (DC-LIN) transceiver.

### **Settings**

LA Channel: Show the selected channel.

**Show Scale:** It will show the scales according to the bit width on the waveform. Enabled when checked.

Import LDF File: Enable users to import the LIN Description File. Click on Add

and select LDF file.

**Version:** Different versions can be selected for LIN analysis. The Checksum verification after Lin version 2.0 has changed to two modes. If user need to use the enhanced verification below, user should select the version after 2.0 to use it.

**Baud rate:** Show the selected baud rate.

**Checksum Mode:** Select the proper baud rate of the signal before the analysis. When set to auto, it will automatically detect the baud rate that matches the signal to be analyzed.

#### Result

### The decoder with LDF

# **Line Decoding**

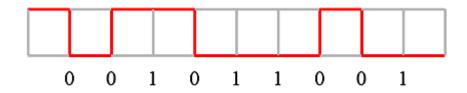

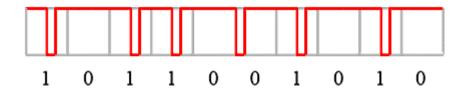

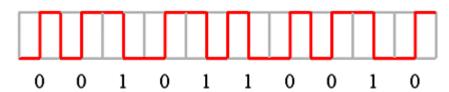

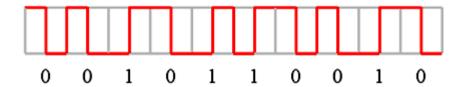

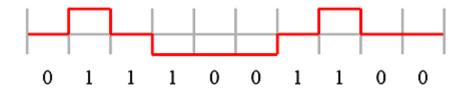

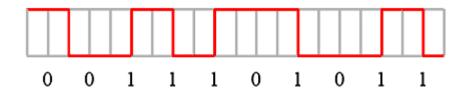

NRZI (Non return to zero, inverted): Non return to zero, inverted (NRZI) is a method of mapping a binary signal to a physical signal for transmission over some transmission media. The two level NRZI signal has a transition at a clock boundary if the bit being transmitted is a logical one, and does not have a transition if the bit being transmitted is a logical zero. There are two modes:

NRZI (Transition occurs for a one): A 1 is represented by a transition of the physical level, a 0 has no transition.

**NRZI (Transition occurs for a zero):** A 0 is represented by a transition of the physical level, a 1 has no transition.

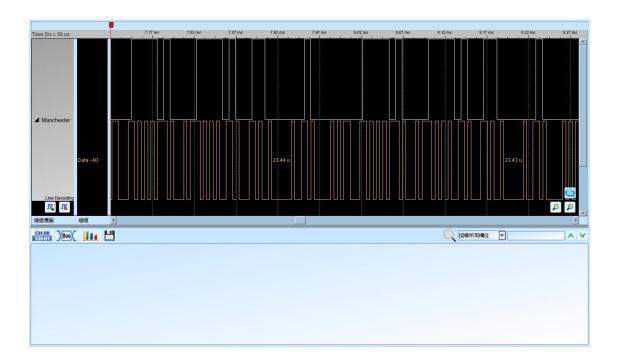

**Manchester:** In telecommunication, Manchester code is a line code in which the encoding of each data bit has at least one transition and occupies the same time. It is, therefore, self-clocking, which means that a clock signal can be recovered from the encoded data. There are three modes:

**Manchester (Thomas):** A 0 is expressed by a low-to-high transition, a 1 by high-to-low transition.

**Manchester (IEEE802.3):** A 1 is expressed by a low-to-high transition, a 0 by high-to-low transition.

**Differential Manchester:** A 1 bit is indicated by making the first half of the signal equal to the last half of the previous bit's signal i.e. no transition at the start of the bit-time. A '0' bit is indicated by making the first half of the signal opposite to the last half of the previous bit's signal i.e. a zero bit is indicated by a transition at the beginning of the bit-time. In the middle of the bit-time there is always a transition, whether from high to low, or low to high. A reversed scheme is possible, and no advantage is given by using either scheme.

**Bi-phase Mark:** The bi-phase mark code (also called FM1 code) is a type of encoding for binary data streams. When a binary data stream is sent without modification via a channel, there can be long series of logical ones or zeros without any transitions which makes clock recovery and synchronization difficult.

When encoding, the symbol rate must be twice the bitrate of the original signal.

Every bit of the original data is represented as two logical states that together form a bit.

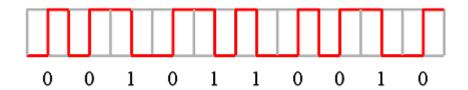

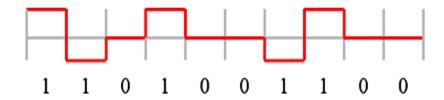

Miller: Delay encoding is also known as Miller encoding.

In telecommunications, delay encoding is the encoding of binary data to form a two-level signal such that (a) a "0" causes no change of signal level unless it is followed by another "0" in which case a transition to the other level takes place at the end of the first bit period; and (b) a "1" causes a transition from one level to the other in the middle of the bit period.

Delay encoding is used primarily for encoding radio signals because the frequency spectrum of the encoded signal contains less low-frequency energy than a conventional non-return-to-zero (NRZ) signal and less high-frequency energy than a bi-phase signal.

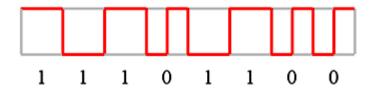

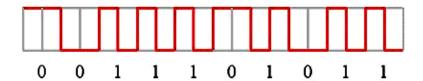

**Modified Miller:** The Modified Miller (M 2) demodulator facilitates demodulation of M 2 modulation data to NRZ-L (non-return-to-zero-level) data, composed of a data separation circuit for producing synchronizing clock pulses from the M 2 modulation data which is reproduced by a data recording device and separating the M 2 modulation data into clock bits and data bits, and an M 2 modulation

data demodulation circuit for producing NRZ - L data by utilizing the clock bits, data bits and synchronizing clock pulses which are output from the data separation circuit.

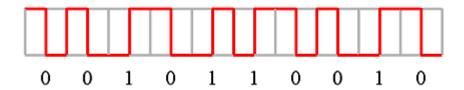

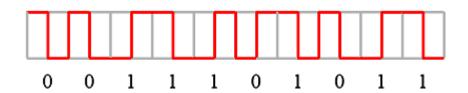

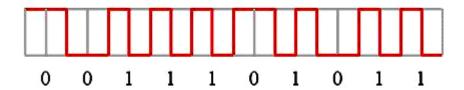

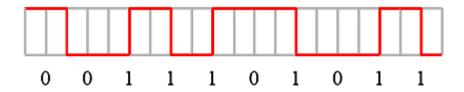

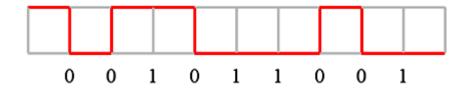

This structure enables the M 2 modulation data which is input to the M 2 demodulation circuit to be easily demodulated to an NRZ - L type data signal by means of a very simple circuit structure. An example is as below:

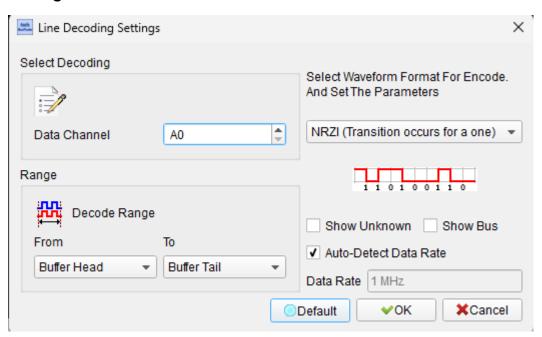

### **Settings**

**Select Decoding:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

Select the line code that user want to decode:

- I. NRZI (Transition occurs for a one)

- II. NRZI (Transition occurs for a zero)

- III. Manchester (Thomas)

IV. Manchester (IEEE802.3)

V. Differential Manchester

VI. Biphase Mark Decode

VII. Miller

VIII. Modified Miller

**Show Unknown:** Display unknown data.

**Show Bus:** Display bus data.

Auto-Detect Data Rate: Enter the Data Rate manually if the Auto-Detect Date

Rate is not selected.

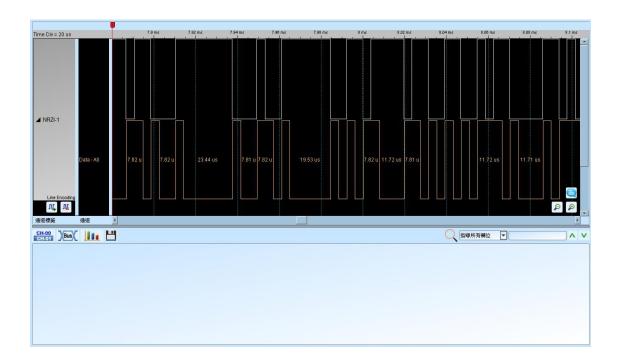

# **Line Encoding**

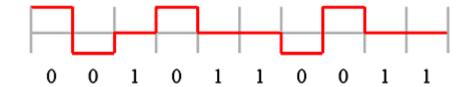

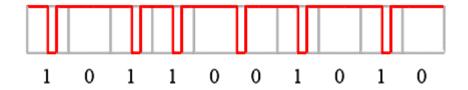

NRZI (Non return to zero, inverted): Non return to zero, inverted (NRZI) is a method of mapping a binary signal to a physical signal for transmission over some transmission media. The two level NRZI signal has a transition at a clock boundary if the bit being transmitted is a logical one, and does not have a transition if the bit being transmitted is a logical zero. There are two modes:

NRZI (Transition occurs for a one): A 1 is represented by a transition of the physical level, a 0 has no transition.

**NRZI (Transition occurs for a zero):** A 0 is represented by a transition of the physical level, a 1 has no transition.

**Manchester:** In telecommunication, Manchester code is a line code in which the encoding of each data bit has at least one transition and occupies the same time. It is, therefore, self-clocking, which means that a clock signal can be recovered from the encoded data. There are three modes:

**Manchester (Thomas):** A 0 is expressed by a low-to-high transition, a 1 by high-to-low transition.

**Manchester (IEEE802.3):** A 1 is expressed by a low-to-high transition, a 0 by high-to-low transition.

Differential Manchester: A 1 bit is indicated by making the first half of the signal equal to the last half of the previous bit, i.e. no transition at the start of the bit-time. A '0' bit is indicated by making the first half of the signal opposite to the last half of the previous bit's signal i.e. a zero bit is indicated by a transition at the beginning of the bit-time. In the middle of the bit-time there is always a transition, whether from high to low, or low to high. A reversed scheme is possible, and no advantage is given by using either scheme.

**AMI (Alternate Mark Inversion):** There are four modes:

**AMI (Standard):** AMI (Alternate Mark Inversion) is a synchronous clock encoding technique that uses bipolar pulses to represent logical 1 value. It is therefore a three level system. A logical 0s is represented by no symbol, and a logical 1 is represented by alternating-polarity pulses.

AMI (B8ZS): Bipolar-8-Zero Substitution

If 1 is +, 00000000 is represented to 000+-0-+

1 is -, 00000000 is represented to 000-+0+-

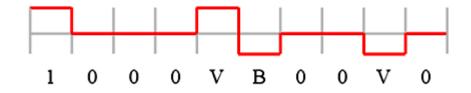

## AMI (HDB3): High Density Bipolar 3

The HDB3 code is a bipolar signaling technique (i.e. relies on the transmission of both positive and negative pulses). It is based on Alternate Mark Inversion (AMI), but extends this by inserting violation codes whenever there is a run of 4 or more 0's. This and similar (more complex) codes have replaced AMI in modern distribution networks. The encoding rules follow those for AMI, except that sequences of four consecutive 0's are encoding using a special "violation" bit. This bit has the same polarity as the last 1-bit which was sent using the AMI encoding rule. The purpose of this is to prevent long runs of 0's in the data stream that may otherwise prevent a DPLL from tracking the center of each bit. Such a code is sometimes called a "run length limited" code, since it limits the runs of 0's that would otherwise be produced by AMI. One refinement is necessary, to prevent a dc voltage being introduced by excessive runs of zeros. This refinement is to encode any pattern of more than four bits as B00V, where B is a balancing pulse. The value of B is assigned as + or -, so as to make alternate "V"s of opposite polarity. The receiver removes all Violation pulses, but in addition a violation preceded by two zeros and a pulse is treated as the "B00V" pattern and both the violation and balancing pulse are removed from the received bit stream. This restores the original bit stream.

**MLT-3: Multilevel Transmission 3:** A 0 means no transition happens, a 1 is represented by a transition (0, +, 0, -).

**Pseudoternary:** A 1 is always zero, a 0 is represented by a transition (+, -).

**CMI (Coded Mark Inversion):** A zero is sent a low to high [01] transition, while a one is sent as either a one [1] or zero [0] depending on the previous state. If the previous state was high the one is sent as a zero [0], if it was low the one is sent as a one [1].

**Bi-phase Mark:** The bi-phase mark code (also called FM1 code) is a type of encoding for binary data streams. When a binary data stream is sent without modification via a channel, there can be long series of logical ones or zeros without any transitions that make clock recovery and synchronization difficult. When encoding, the symbol rate must be twice the bitrate of the original signal. Every bit of the original data is represented as two logical states that form a bit.

Miller: Delay encoding is also known as Miller encoding.

In telecommunications, delay encoding is the encoding of binary data to form a two-level signal such that (a) a "0" causes no change of signal level unless it is followed by another "0" in which case a transition to the other level takes place at the end of the first bit period; and (b) a "1" causes a transition from one level to the other in the middle of the bit period.

Delay encoding is used primarily for encoding radio signals because the frequency spectrum of the encoded signal contains less low-frequency energy than a conventional non-return-to-zero (NRZ) signal and less high-frequency energy than a bi-phase signal.

**Modified Miller:** The Modified Miller (M 2) demodulator facilitates demodulation of M 2 modulation data to NRZ-L (non-return-to-zero-level) data, composed of a data separation circuit for producing synchronizing clock pulses from the M 2 modulation data which is reproduced by a data recording device and separating the M 2 modulation data into clock bits and data bits, and an M 2 modulation data demodulation circuit for producing NRZ - L data by utilizing the clock bits, data bits and synchronizing clock pulses which are output from the data separation circuit.

This structure enables the M 2 modulation data which is input to the M 2 demodulation circuit to be easily demodulated to an NRZ - L type data signal by means of a very simple circuit structure. An example is as below:

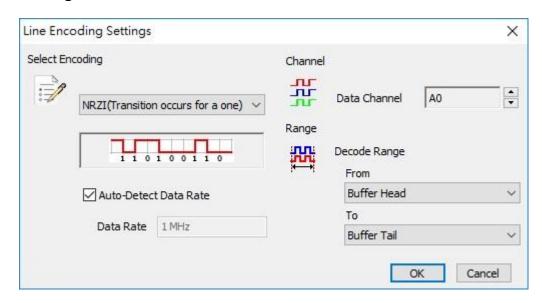

## **Settings**

**Select Encoding:** Set the channel number of the Logic Analyzer to which each signal end is connected on the object to be tested.

Select the line code you want to encode:

- I. NRZI (Transition occurs for a one)

- II. NRZI (Transition occurs for a zero)

- III. Manchester (Thomas)

- IV. Manchester (IEEE802.3)

- V. Differential Manchester

- VI. AMI (Standard)

- VII. AMI (B8ZS)

VIII. AMI (HDB3)

IX. Pseudoternary

X. MLT-3

XI. CMI

XII. Biphase Mark Encode

XIII. Miller

XIV. Modified Miller

**Auto-Detect Data Rate:** Enter the Data Rate manually if the Auto-Detect Date Rate is not selected.

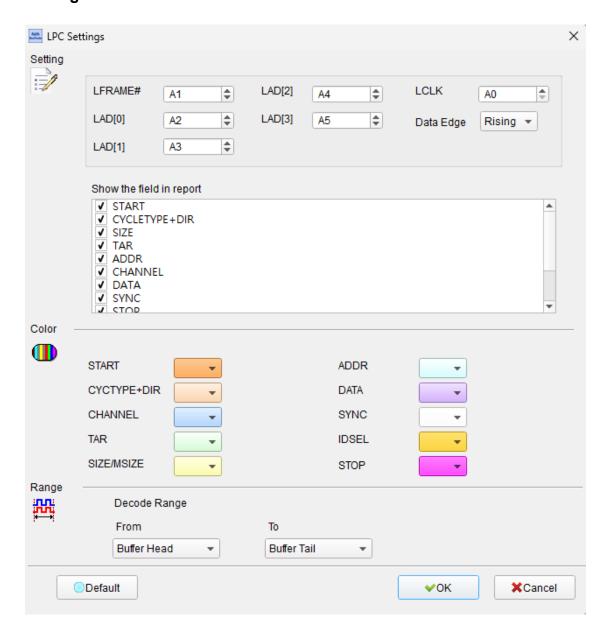

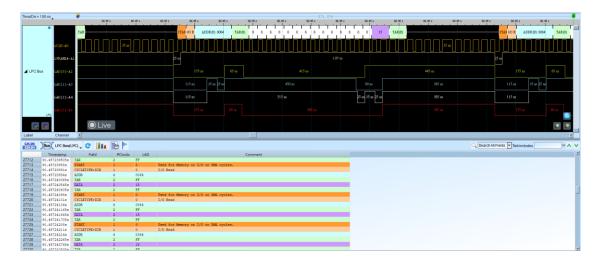

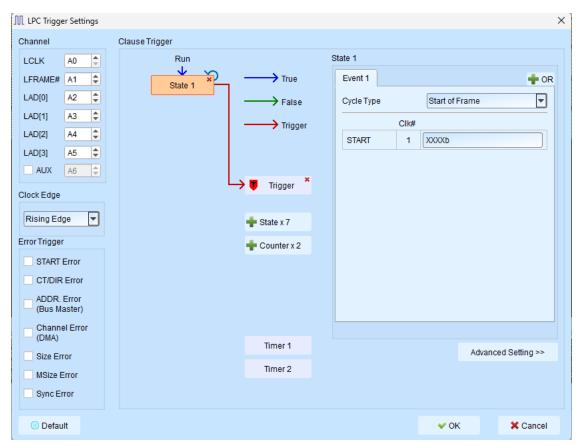

#### **LPC**

The LPC bus, for the data transmissions, was developed by Intel to replace the ISA bus.

## **Settings**

LCLK: Transfer clock of LPC.

**Data Edge:** Latch the data to be analyzed when the LCLK is rising or falling.

LFRAME#: Marks the start of each Frame transfer cycle or is used to interrupt

Frame transfer.

**LAD[0-3]:** The data bus is used to transfer commands, addresses, and data.

**Show the field in report:** To enable report filtering, simply check the items to be displayed in the report window.

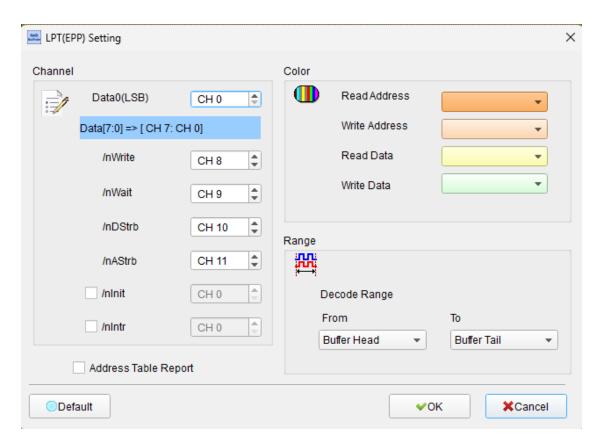

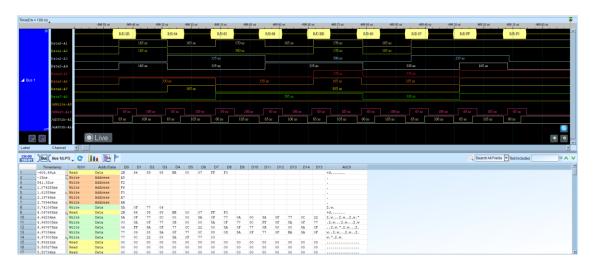

#### **LPT**

LPT is a universal parallel interface that use in PC since 1980's. It was primarily designed to operate a line printer, but could also be used to adapt other peripherals. This decode only support EPP Mode.

### **Settings**

**Data0(LSB):** There are 8 data channel. Only set Data0(LSB) here, other channel will be set automatically.

/nWrite: Indicates the direction of transfer.

**/nWait:** To acknowledge that a transfer has finished.

/nDStrb: Indicates the data cycle.

/nAStrb: Indicates the address cycle.

/nInit: Indicates a termination cycle in order to return the interface to the

Compatibility mode. User can option to use this channel or not.

/nIntr: This is an interrupt signal. User can option to use this channel or not.

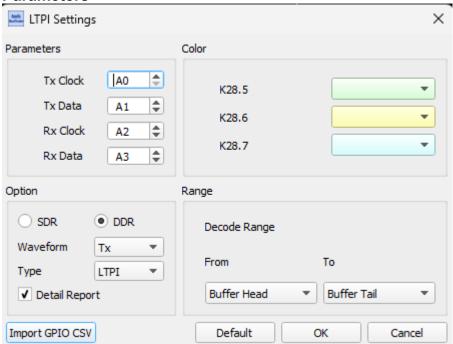

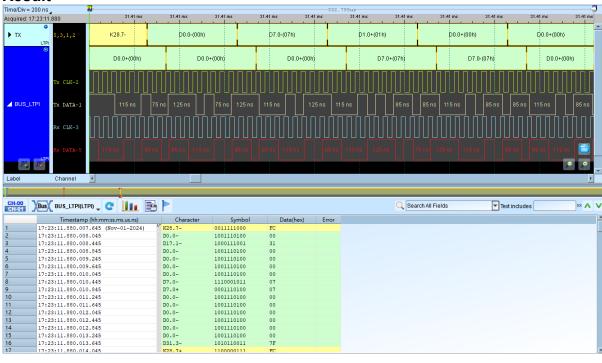

#### **LTPI**

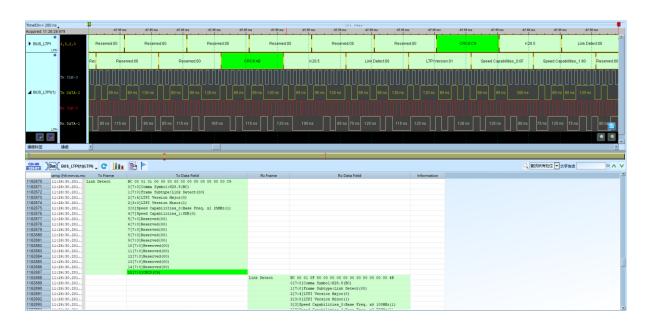

LTPI (LVDS Tunneling Protocol & Interface) is an interface protocol designed for transmitting low-speed signals between the HPM (Host Processor Module) and SCM (Server Control Module). It supports multiple channels such as GPIO, I2C/SMBus, and UART, utilizing time-division multiplexing (TDM) over LVDS links to achieve multi-channel transmission. The GPIO channel includes both low-latency and normal-latency types. The I2C/SMBus channel handles single-controller communication links. The UART channel supports flow control. Additionally, an OEM channel is provided for proprietary interfaces, and a data channel supports memory image data transfers

#### **Parameters**

Tx Clock: Transfer Clock of Tx.

Tx Data: Transfer Data of Tx

Rx Clock: Transfer Clock of Rx

Rx Data: Transfer Data of Tx

**SDR:** The transmission method is SDR •

**DDR:** The transmission method is DDR •

Waveform: The direction (Transmit / Receive) and decoded content displayed

in the waveform area (8b10b / LTPI / GPIO / UART / I2C)

**Detail Report:** Whether to enable detailed reporting

Import GPIO CSV: Whether to import the GPIO bit name

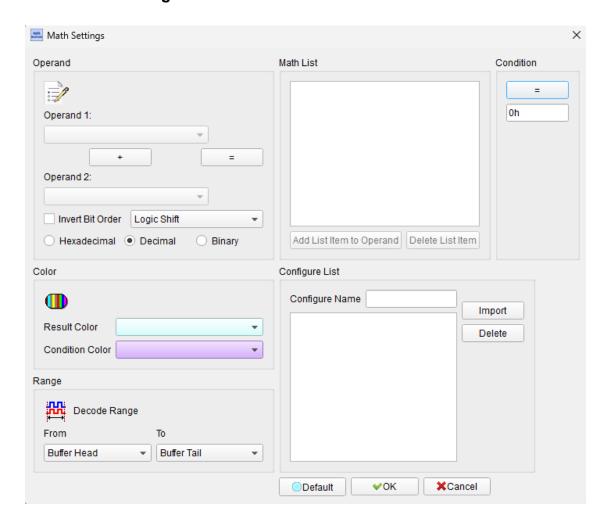

#### Math

Math is used to conduct addition, subtraction, multiplication, division, AND, XOR, OR, NAND, NOR, XNOR, Bit Shift operation for the combined value of channel or bus.

### **Parameters Settings**

### 1. Channels Settings

Operand: The channel or bus for which the calculation is to be performed is automatically listed with the labeled name of the channel or bus in the current waveform window.

- ii. Operator: We support

- 1. Arithmetic operator: + \ \ \ \ /

- 2. Logic operator: AND \ XOR \ OR \ NAND \ NOR \ XNOR \ >> \ <<

- iii. 「=」 button: Add the equation to the Math List

- iv. Invert Bit Order: By default, when adding a new bus, the smaller channel number is Isb and the larger channel number is msb.Users can reverse the order of Isb and msb by setting this option.

- v. Bit Shift Method: We support (i)Arithmetic Shift `(ii)Logic Shift `(iii)

Rotate Circular Shift and (iv)Rotate through Carry Shift. Use with

>> and << in logical operators.

- vi. Numeric Display: We support Hexadecimal . Decimal . Binary.

- vii. Math List: Displaying the equations added by the user, up to a limit of 8.

- viii. 「Add List Item to Operand」 button: Adding the selected item from Math List to operand for user to select for further operating with other channel or bus. Those item that was added to operand is enclosed in a set of parentheses when it operates with other operand. Up 2 levels of parentheses are supported.

## 2. Waveform Settings:

- i. Setting the color of frame that represents the calculated result.

- ii. Setting the comparison condition and the frame color that matches the condition.

## 3. Case Settings:

- ii. Comparison Value: Entering the value of the condition to be compared. Supports hexadecimal and decimal representation.

- 4. Configure: Lists all the configure names so that users can quickly switch between different configures. The configure records a list of different equations.

### **Operating Methods**

- After selecting the operand and operator, click "=" to add the equation to the *Math List*.

- 2. Choosing the equations to be operated on.

- 3. Setting the color of frame that represents the calculated result.

- 4. Setting the comparison condition and entering the comparison value, also setting the color for displaying the matches frame.

### Result

**Note:** After setting, press OK to write all the settings to a file and save it to the working directory (AqMath.bin). The file will be overwritten every time user press OK, so when user save the file, user need to save a copy of AqMath.bin in addition to the waveform file. When user open the waveform file, user need to place AqMath.bin in the working directory before opening the waveform file.

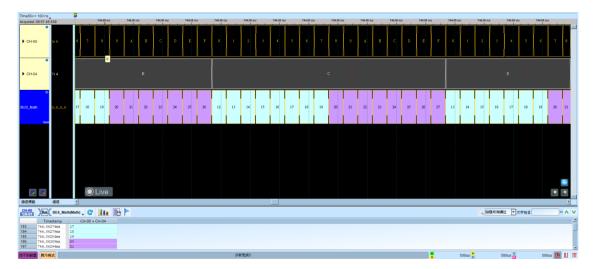

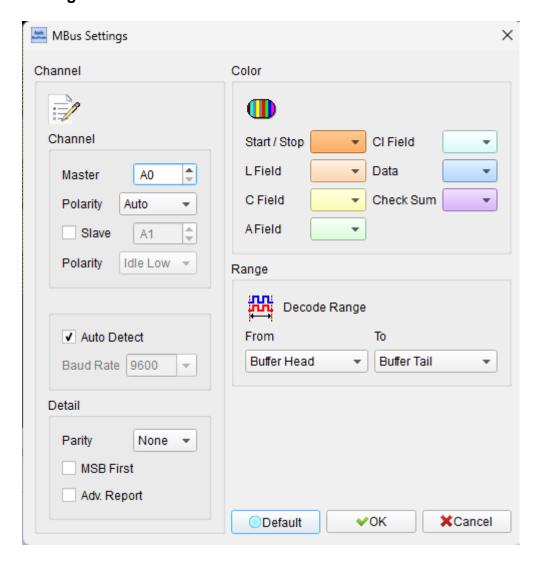

#### M-Bus

M-Bus (Meter-Bus) is for remote reading of heat meters and other types of consumption meters.

## **Settings**

**Channel:** Set the signal channel and polarity. If there is a Slave on the bus, user can set up additional Slave channels. Enable when checked.

**Baud Rate:** The transmission speed of the signal. Checking Auto Detection will detect the baud rate by itself.

#### Detail:

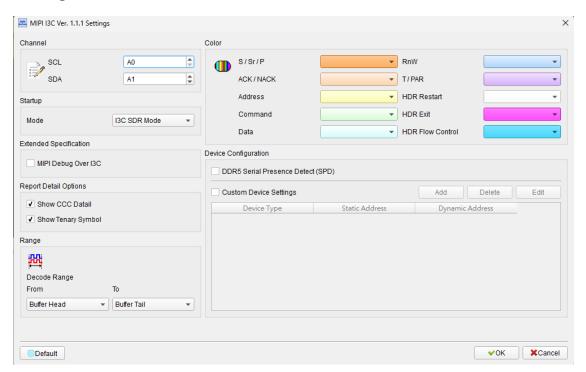

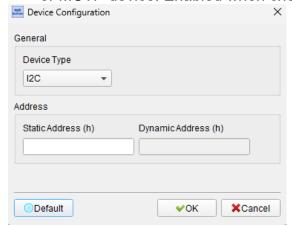

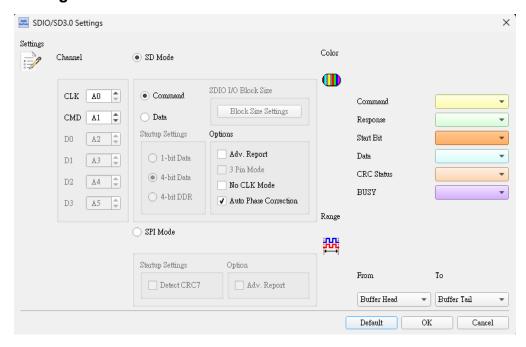

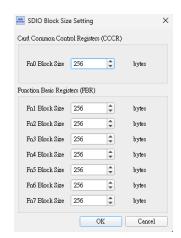

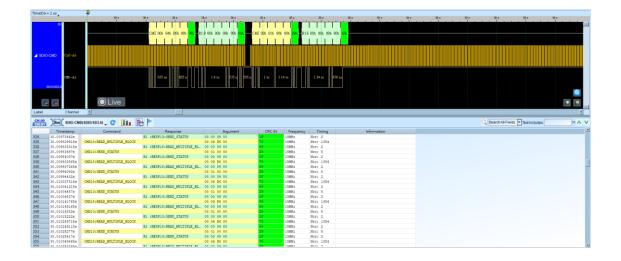

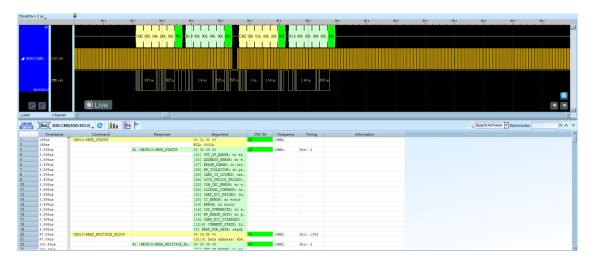

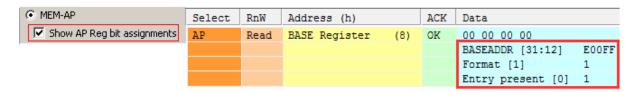

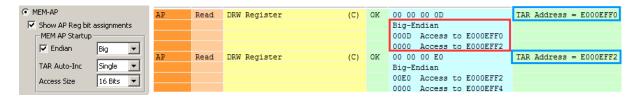

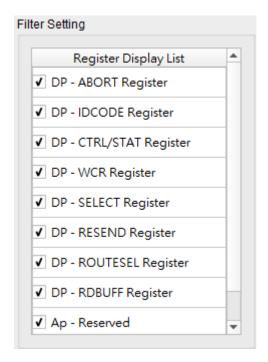

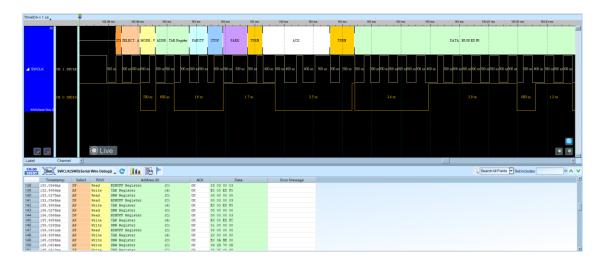

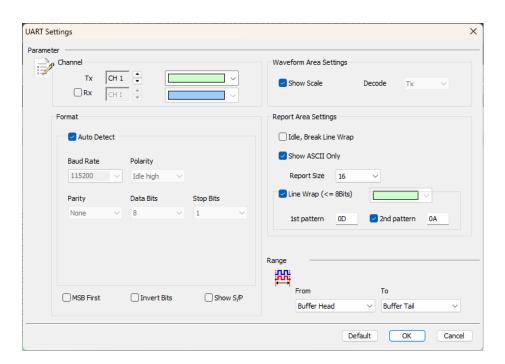

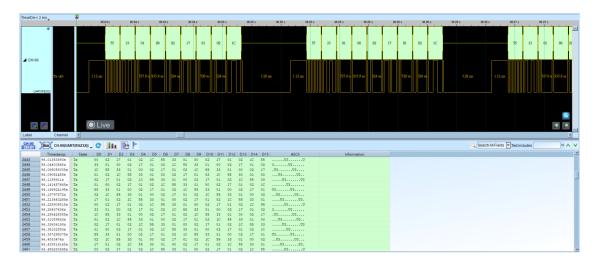

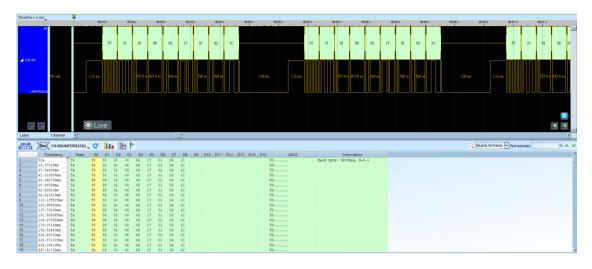

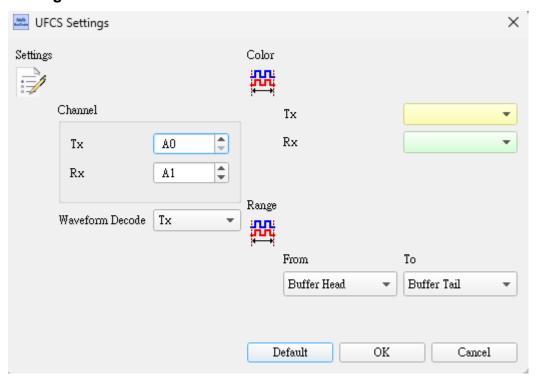

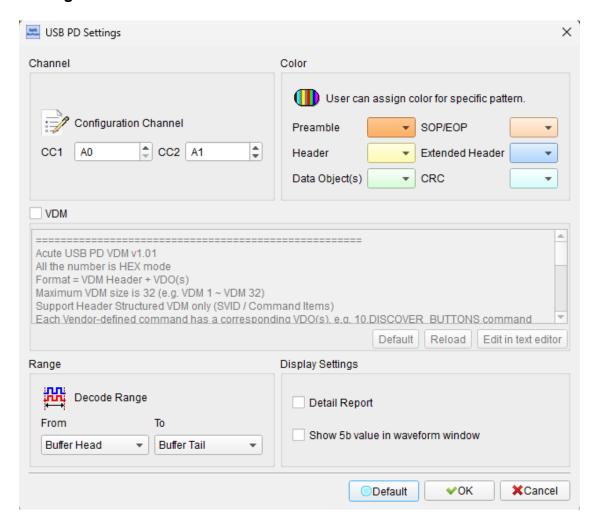

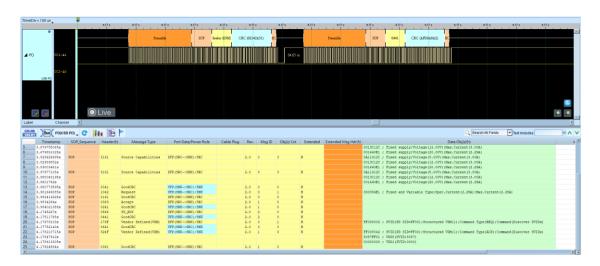

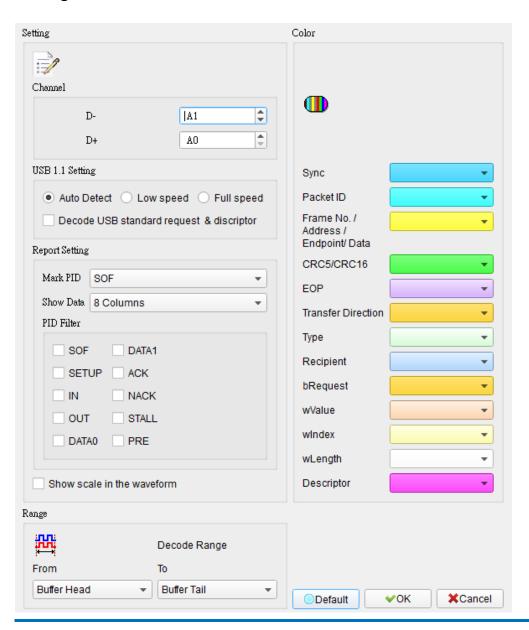

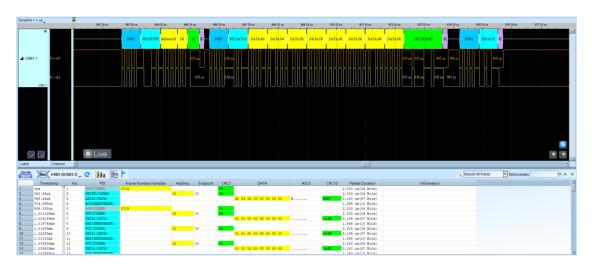

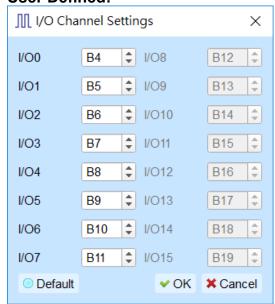

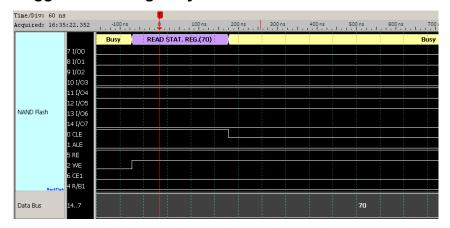

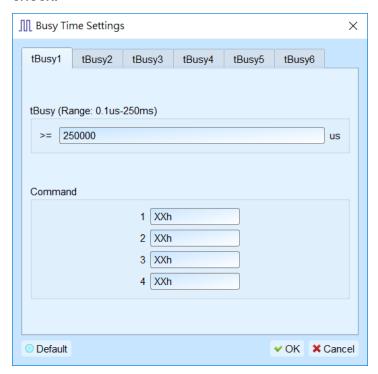

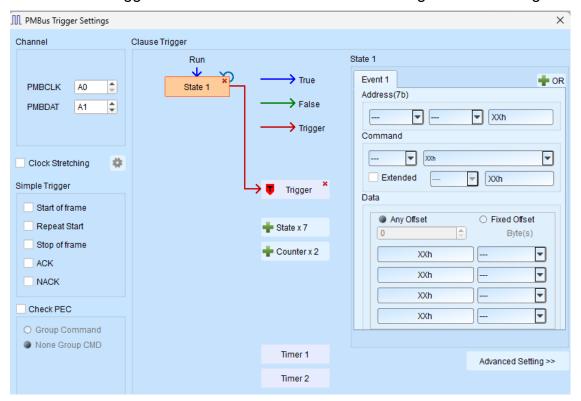

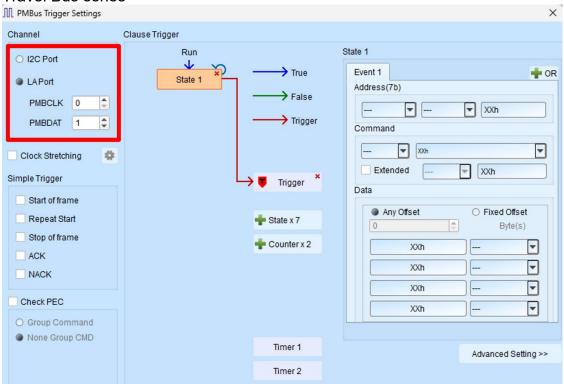

- I. Parity: Parity error detect.