MIPI I3C Electrical Validation

MIPI I3C is backward compatible with many Legacy I2C Devices, but I3C Devices also support higher speed (with SCL clock speed up to 12.5 MHz) and new communication modes. MIPI I3C modes include Single Data Rate (SDR) Mode, High Data Rate (HDR) Mode. HDR Mode is also divided into Dual Data Rate (HDR-DDR) Mode, Ternary Symbol Legacy (HDR-TSL) Mode, Ternary Symbol Pure-bus (HDR-TSP) Mode, and Bulk Transport (HDR-BT) Mode.

MIPI I3C Electrical Validation offers various electrical measurements compliance testing as specified in the MIPI I3C Specification (currently supports MIPI I3C version 1.1.1).

Supported Models:

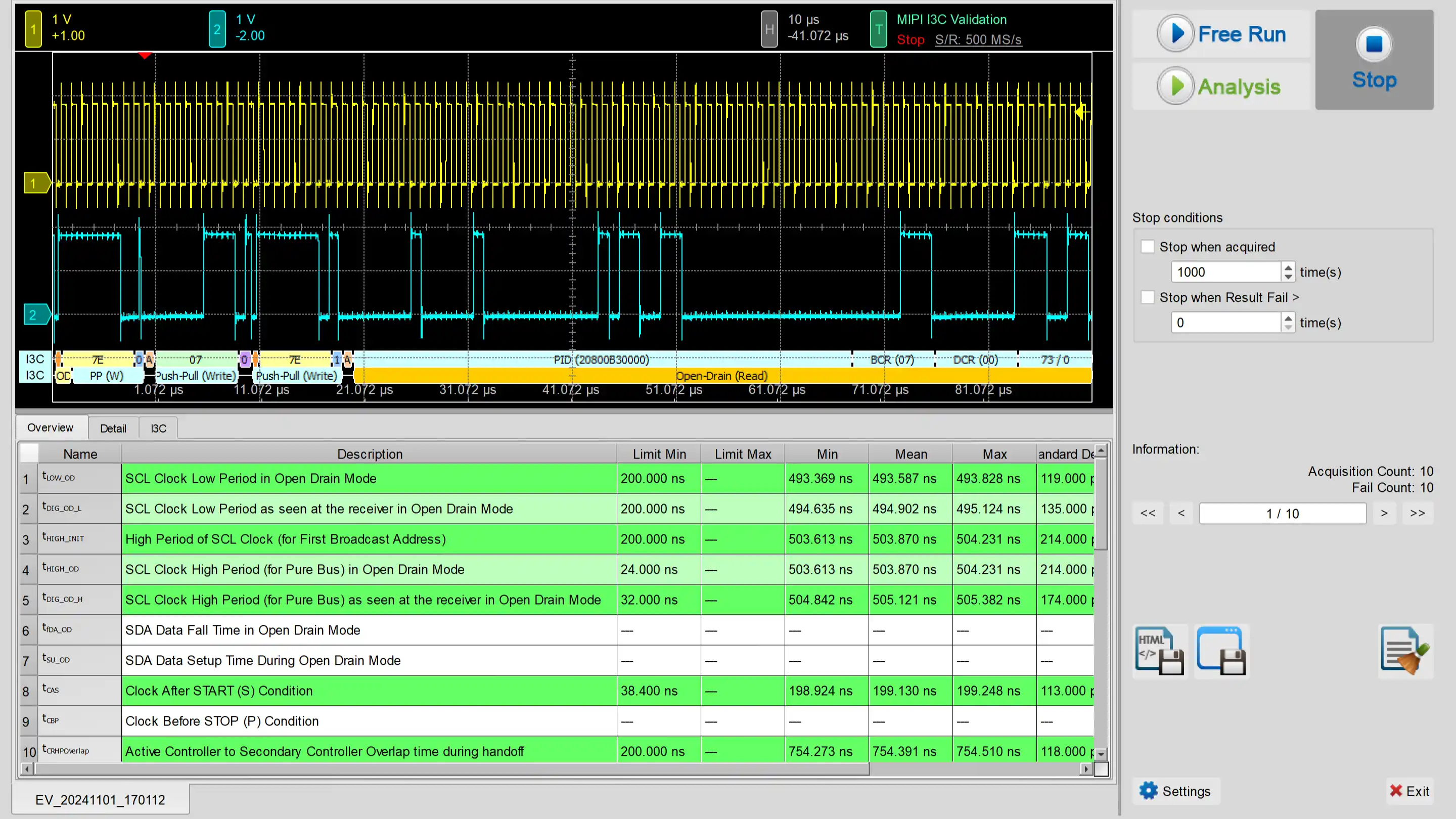

Overview Report

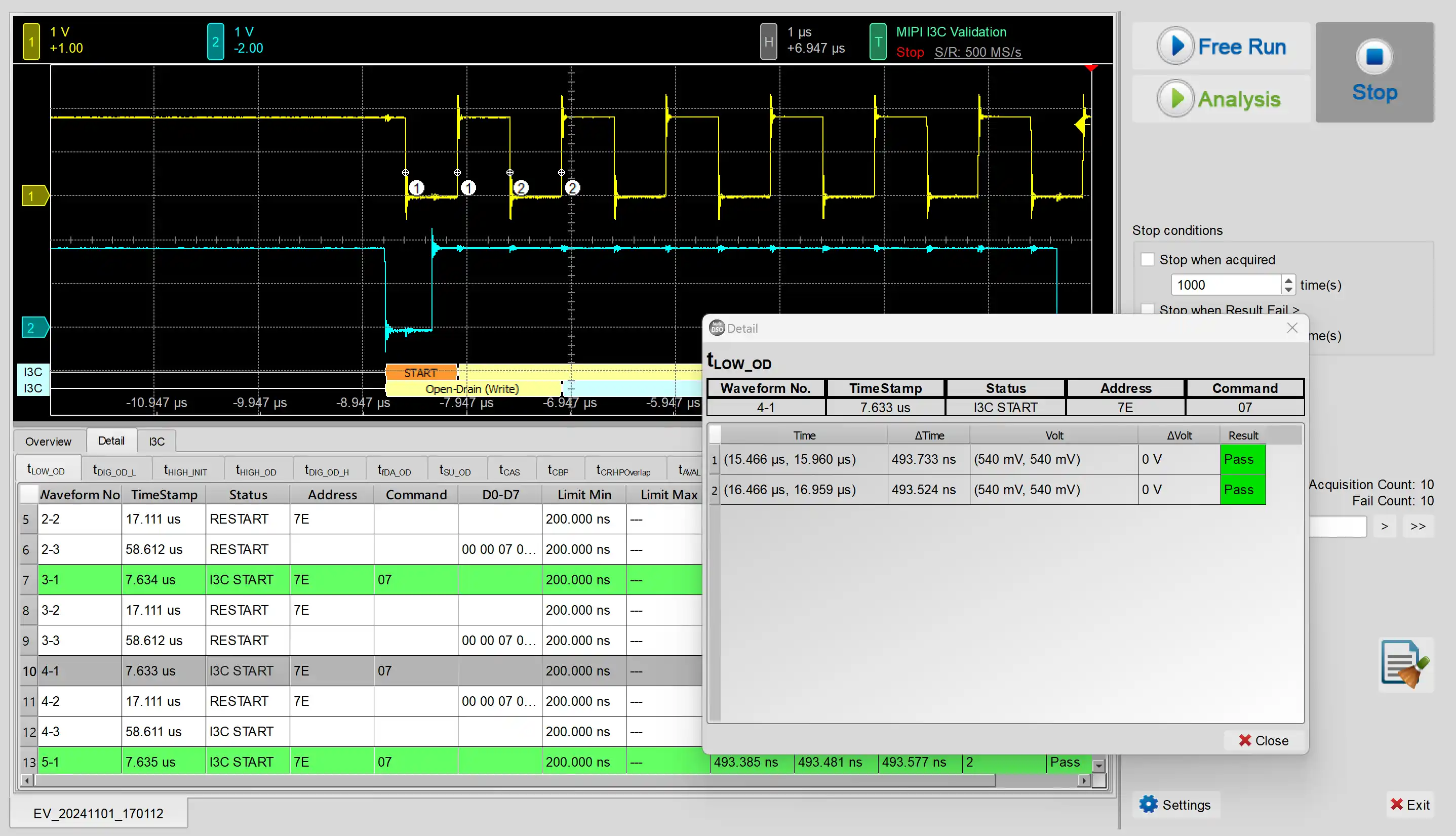

Reference Point Dialog & Waveform:

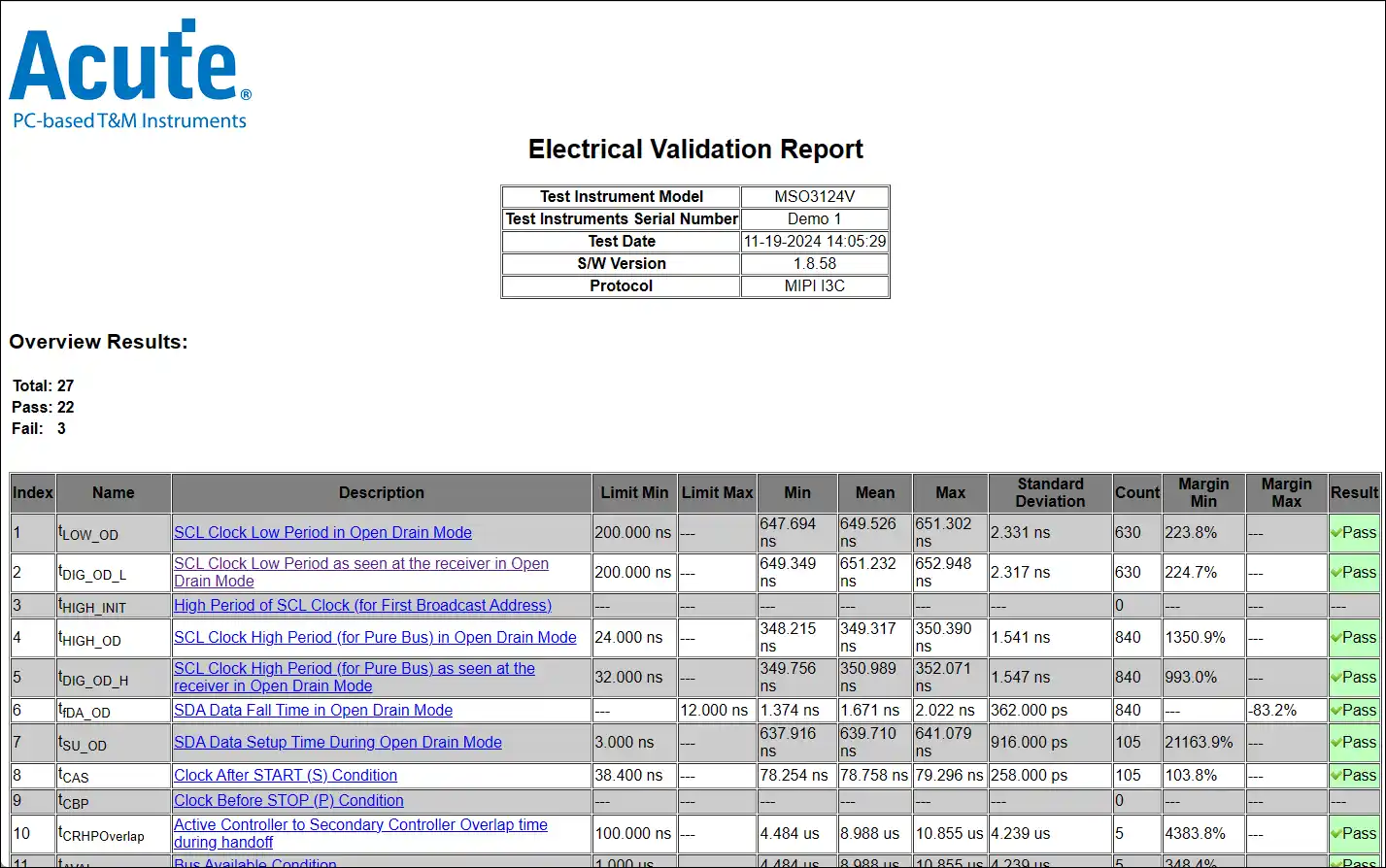

HTML Report

I3C Electrical Validation Settings:

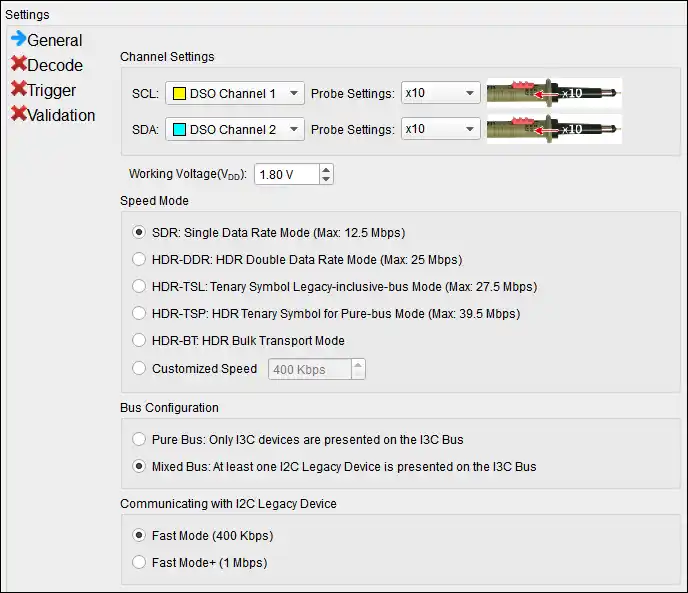

1. General Settings: Channel sources, working voltage and speed

In the General Settings section, the selection of Speed Mode determines a suitable sample rate for validation, but also affects the timing specification table in the validation settings section. For instance, in HDR-TSL and HDR-TSP Mode, there are additional timing specifications listed in the table.

Furthermore, the Bus Configuration section specifies the devices you connected on the I3C Bus. If it is a Pure-Bus setup, I2C timing table is thus not required, which is discussed in the Validation Settings section. On the other hand, a Mixed Bus setup will include the timing table for I2C Legacy Devices, and there default timing values are determined by using Fast Mode (Fm) or Fast Mode (Fm+) configuration, which is an identical settings to I2C Electrical Validation setup.

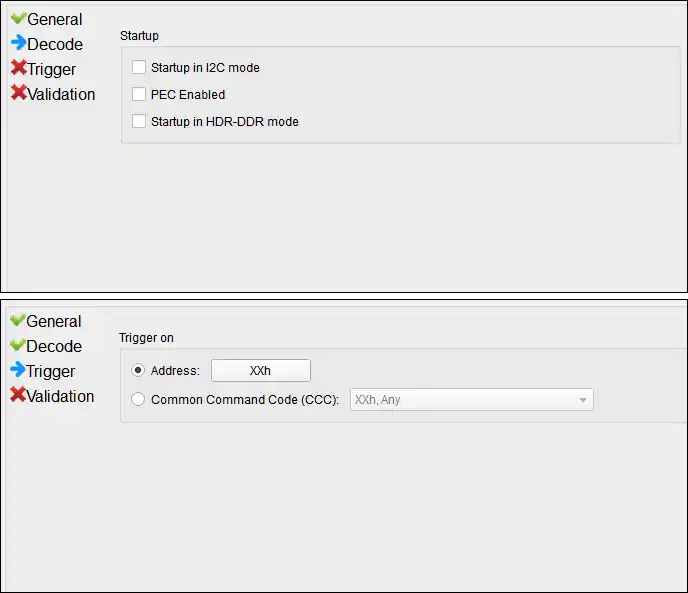

2~3. Decode / Trigger Settings:

If you are interested in analyzing specific devices address, set the trigger address to the value you prefer. In the figure above, “XX” stands for don’t care term. Thus, it triggers on all address in this case. It also provides triggering on Common Command Code (CCC), which is specified on the Broadcast Address 7’h7E.

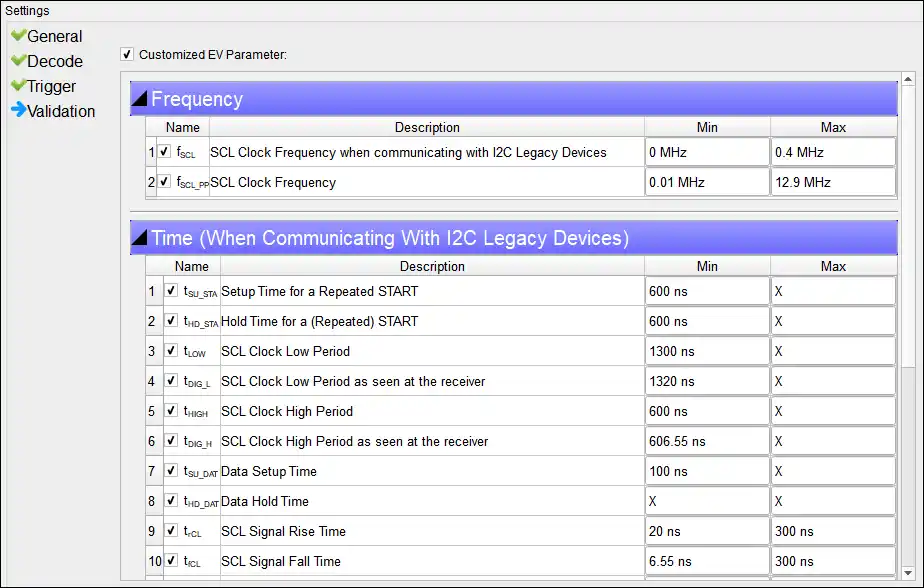

4. Electrical Validation Parameter Settings: Frequency, Timing, Voltage limitation

This section includes 5 parameter tables, including

• Frequency

• I3C timing requirements when communicating with I2C Legacy Devices

• I3C Open Drain timing parameters

• I3C Push-Pull timing parameters

• I3C I/O stage characteristics voltage requirements

In the Pure Bus setup, the timing requirements table with I2C Legacy Devices is not required and thus be hidden from the parameter settings dialog. The frequency parameter fSCL will also be hidden in the Pure Bus setup.

| MIPI I3C Frequency Requirements | |

| Symbol | Electrical Parameter |

| fSCL | SCL Clock Frequency when communicating with I²C Legacy Devices |

| tSCL_PP | SCL Clock Frequency |

| tBT_FREQ | HDR-BT SCL Clock Frequency |

| MIPI I3C Timing Requirements When Communicating With I2C Legacy Devices | |

| Symbol | Electrical Parameter |

| tSU_STA | Setup Time for a REPEATED START |

| tHD_STA | Hold Time for a (REPEATED) START |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSU_DAT | Data Setup Time |

| tHD_DAT | Data Hold Time |

| trCL | SCL Signal Rise Time |

| tfCL | SCL Signal Fall Time |

| trDA | SDA Signal Rise Time |

| trDA_OD | SDA Signal Rise Time (Open Drain) |

| tfDA | SDA Signal Fall Time |

| tSU_STO | Setup Time for STOP |

| tBUF | Bus Free Time Between a STOP and a START |

| tSPIKE | Pulse Width of Spikes that Spike Filter Must Suppress |

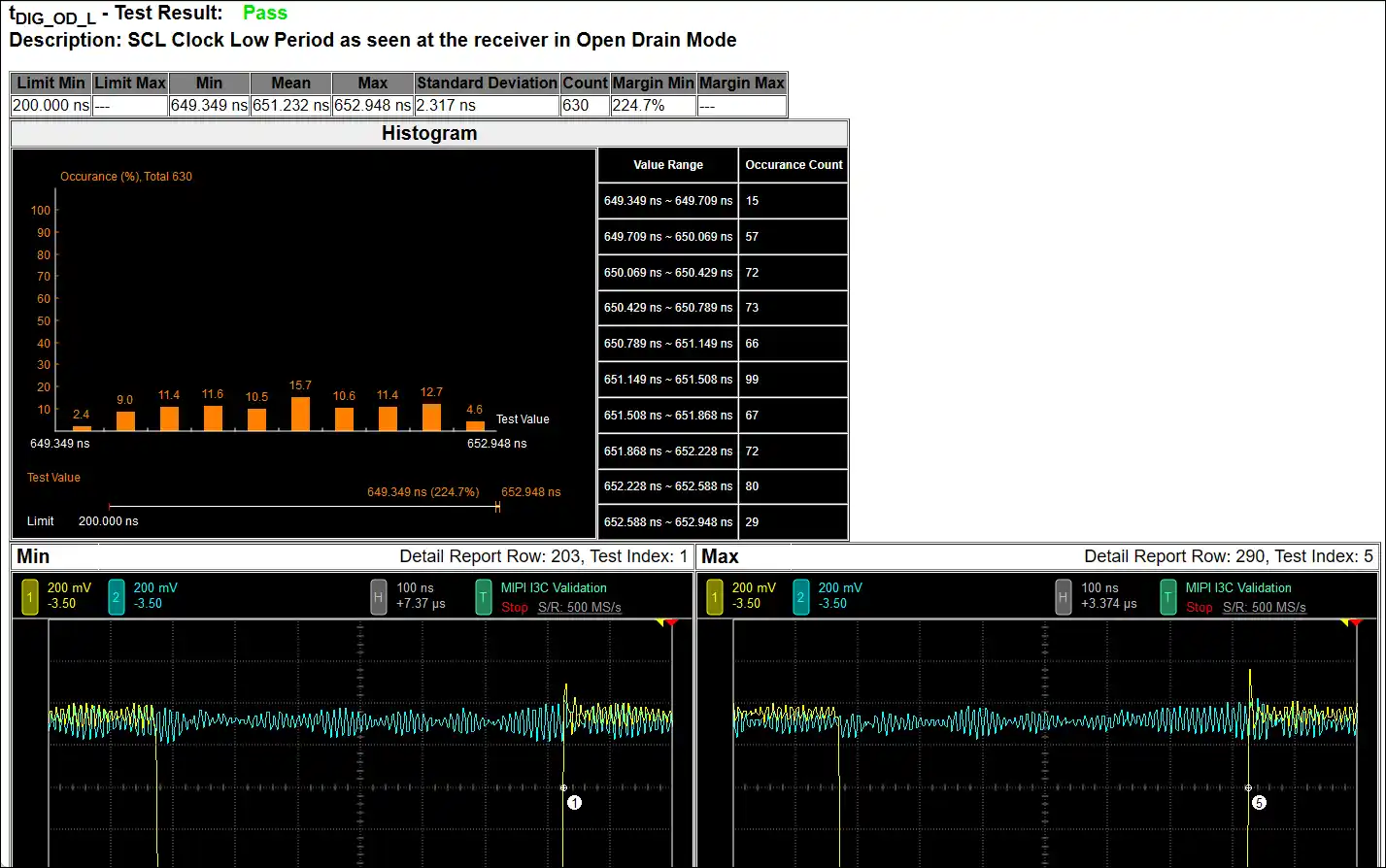

| MIPI I3C Open Drain Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW_OD | SCL Clock Low Period |

| tDIG_OD_L | SCL Clock Low Period as seen at the receiver |

| tHIGH_INIT | High Period of SCL Clock (for First Broadcast Address) |

| tHIGH_OD | SCL Clock High Period |

| tDIG_OD_H | SCL Clock High Period as seen at the receiver |

| tfDA_OD | SDA Data Fall Time |

| tSU_OD | SDA Data Setup Time During Open Drain Mode |

| tCAS | Clock After START (S) Condition |

| tCBP | Clock Before STOP (P) Condition |

| tCRHPOverlap | Active Controller to Secondary Overlap time during handoff |

| tAVAL | Bus Available Condition |

| tIDLE | Bus Idle Condition |

| tNEWCRLock | Time Interval Where New Controller Not Driving SDA Low |

| MIPI I3C Push-Pull Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSCO | Clock in to Data Out for Target |

| tCR_PP | SCL Clock Rise Time |

| tCF_PP | SCL Clock Fall Time |

| tHD_PP_Controller | SDA Signal Data Hold (Controller) |

| tHD_PP_Target | SDA Signal Data Hold (Target) |

| tSU_PP | SDA Signal Data Setup |

| tCASr | Clock After Repeated START (Sr) Condition |

| tCBSr | Clock Before Repeated START (Sr) Condition |

| tBT_HO | HDR-BT Master to Slave Hand Off Delay |

| tBT_STALL | HDR-BT Clocked Not-Ready Data-Block Headers |

| MIPI I3C I/O Stage Characteristics Voltage Requirements | |

| Symbol | Electrical Parameter |

| VIL | Low-Level Input Voltage |

| VIH | High-level Input Voltage |

| VOL | Low-level Output Voltage |

| VOH | High-level Output Voltage |

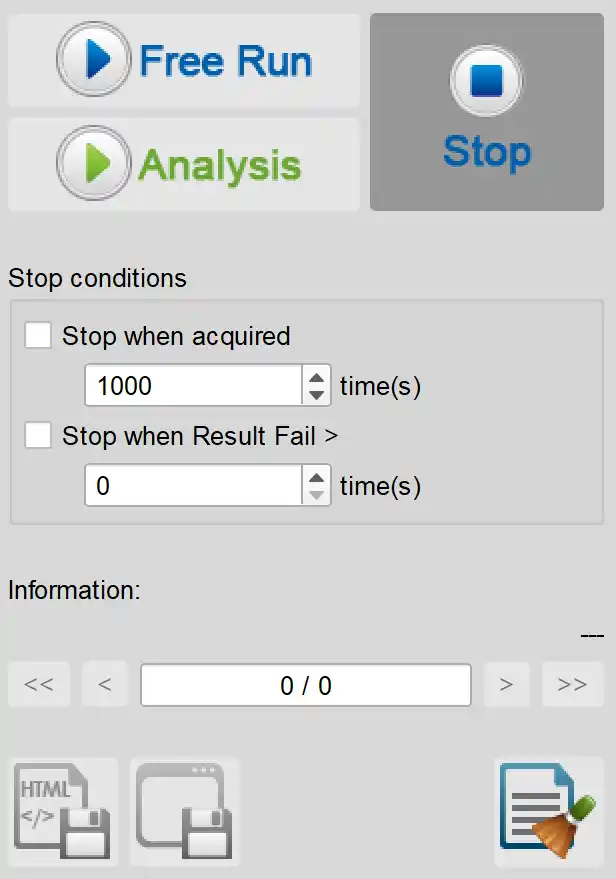

5. Software EV control panel:

Stop Conditions:

Stop when acquired X times

Stop when Result Fail > X times

Information:

Select waveform

Save File:

Save as Html

Save as .MOW (Software format)

YouTube Video