I3C 電氣特性驗證 Electrical Validation

電子設計的關鍵之一是確認電路的正確性和穩定性。在這個背景下,電氣特性驗證功能應運而生,旨在為工程師提供一個全面且便捷的平台,以驗證電子設備的各種電氣特性。

皇晶科技提供的電氣特性驗證功能具有許多優勢,首先是其靈活性和易用性。工程師可以輕鬆設定各種參數,包括電壓、頻率和時序等,而軟體則即時呈現測試結果,包括波形和參考點。更重要的是,軟體還能自動產生詳盡的測試報告,節省了寶貴的時間和人力成本。

此外,在一般設定方面,可以指定訊號來源、工作電壓和速度等關鍵參數,以滿足不同應用場景的需求。解碼設定則可協助更深入的訊號解析,進一步提高了驗證的準確性和可靠性。

此功能還允許工程師對電壓、時序和頻率等關鍵驗證項目進行數值範圍設定,軟體端能夠根據設定內容判斷是否符合範圍,從而確保電子設備在各種條件下的正確性和穩定性。這一功能的引入,為電子設計和驗證工作帶來了全新的效率和便利性,有助於提升產品的品質和可靠性。

支援型號:

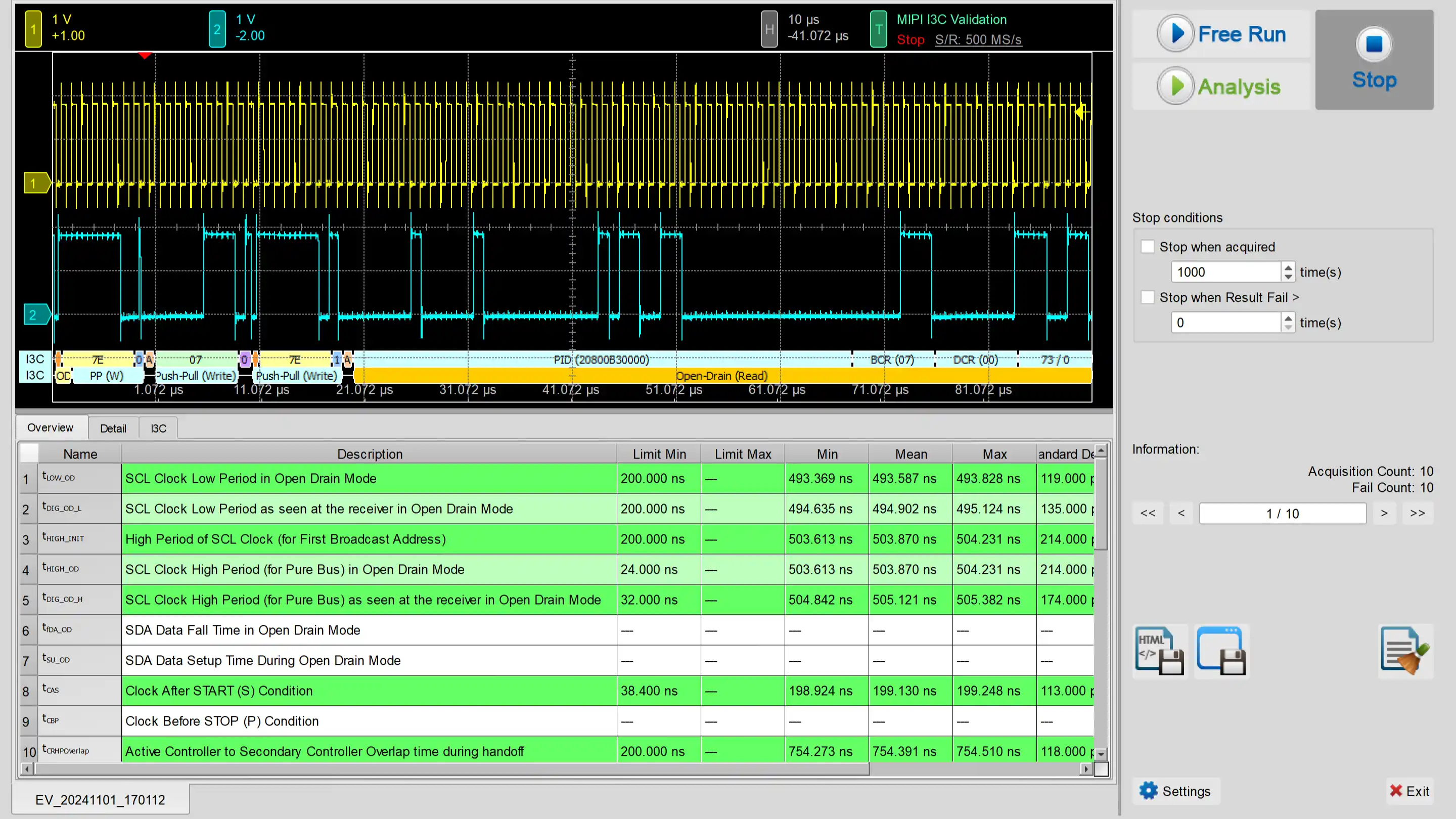

電氣特性驗證 軟體畫面

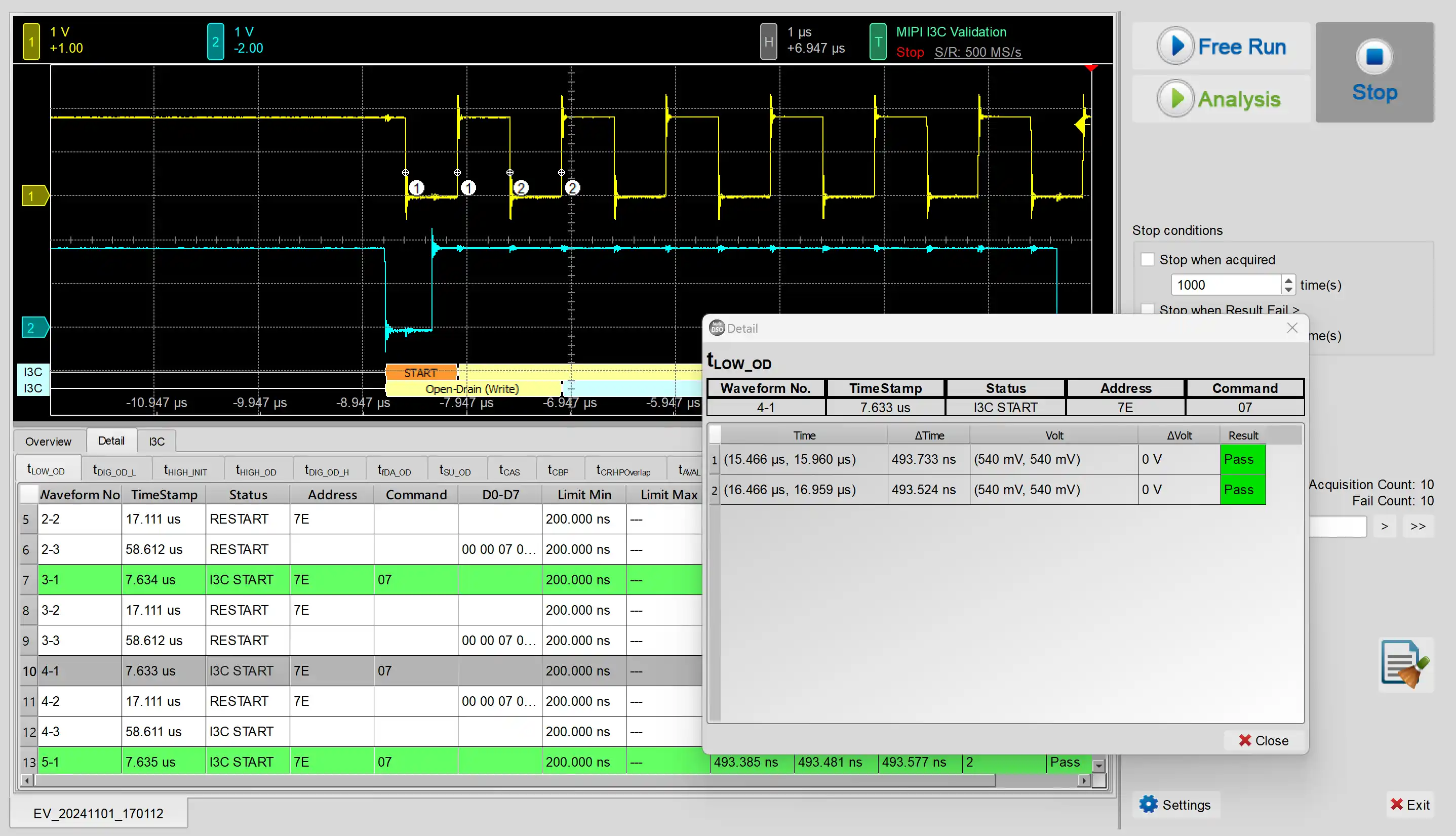

波形和參考點

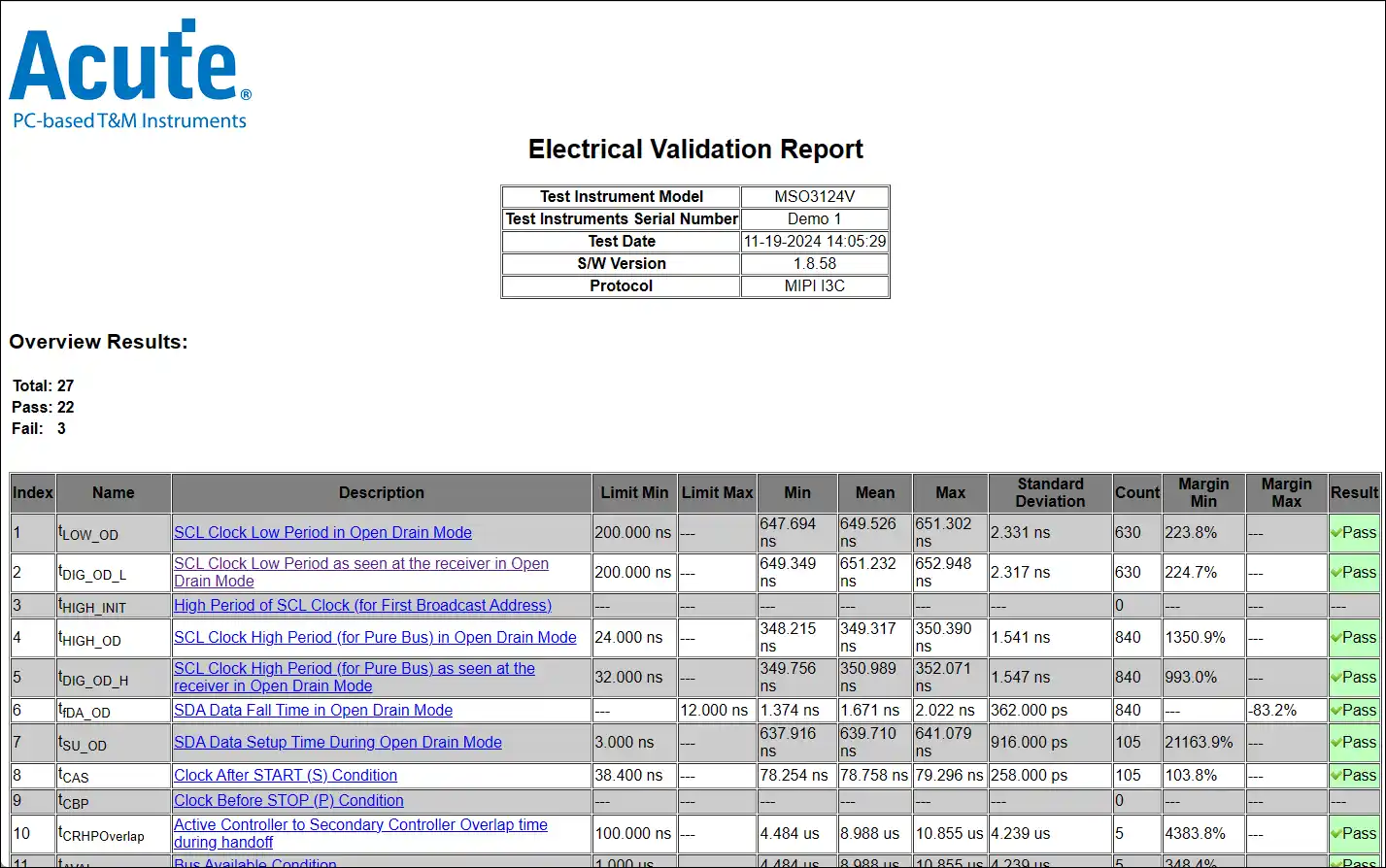

HTML 報告總表 - 有對應連結,可方便輸出/查詢/傳遞

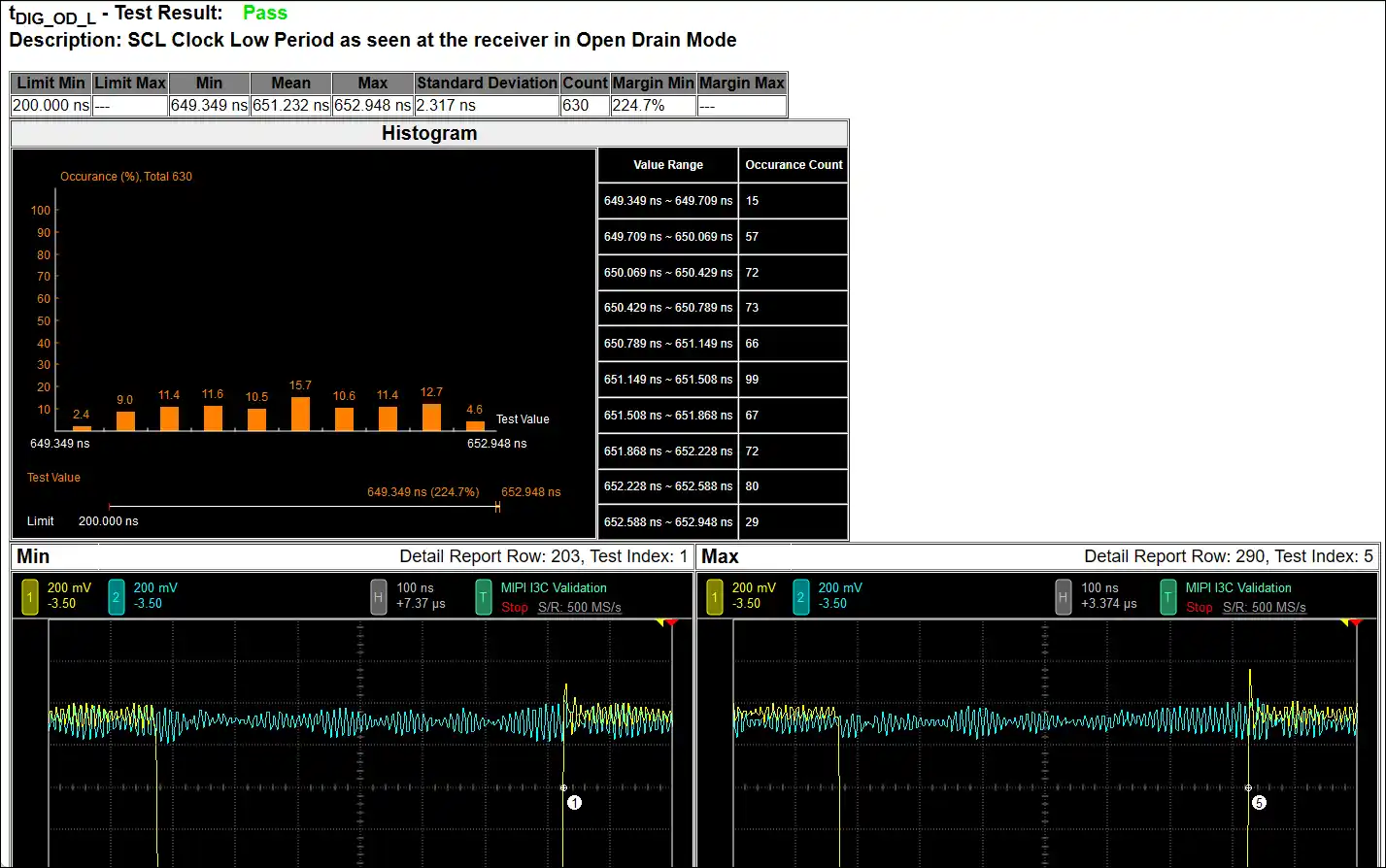

HTML 報告詳細內容

I3C 電氣特性驗證設定:

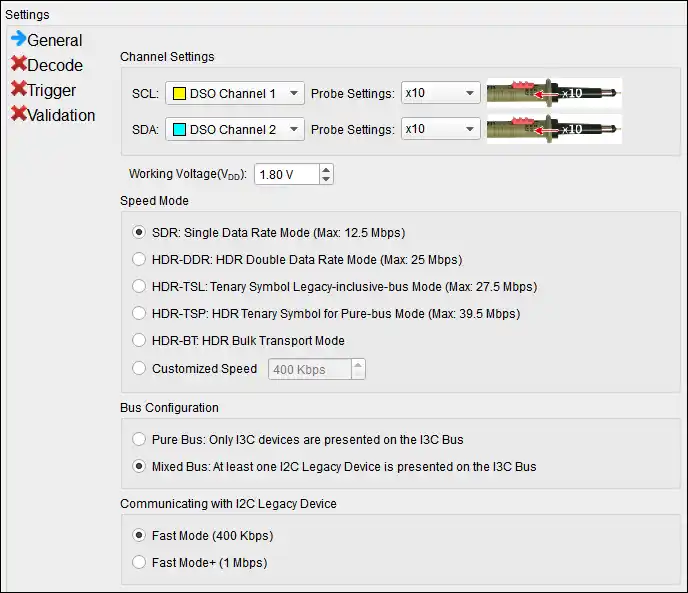

1. General:設定通道來源、工作電壓及速度

在此部分中,所選的速度模式會影響驗證所需的取樣率,同時也會影響後續「驗證設定」部分中的時序規格表。例如,在 HDR-TSL 與 HDR-TSP 模式下,將額外顯示專屬的時序規格。

此外,在「Bus Configuration」中需指定匯流排上連接的裝置類型:

• 純 I3C 匯流排(Pure-Bus):不需要 I²C 時序規格。

• 混合匯流排(Mixed Bus):需加入 I²C 相容裝置的時序規格,預設值採用 Fast Mode(Fm)或 Fast Mode+(Fm+)設定,與 I²C 驗證設定相同。

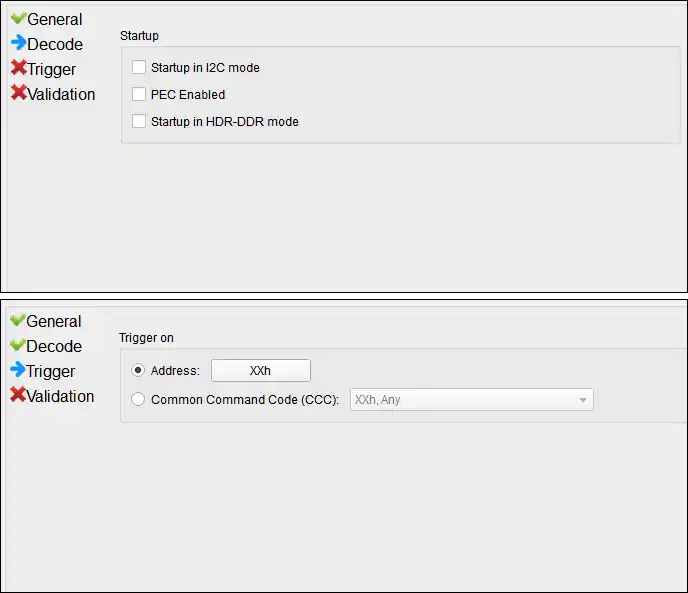

2~3. Decode / Trigger:I3C 解碼 / 觸發 設定

若需要分析特定裝置位址,可設定特定位置為觸發條件。如圖中 "XX" 表示「任意」的位元,將會觸發所有位址。此外亦支援針對常用命令碼(CCC)的觸發,可透過廣播位址 7"h7E 指定。

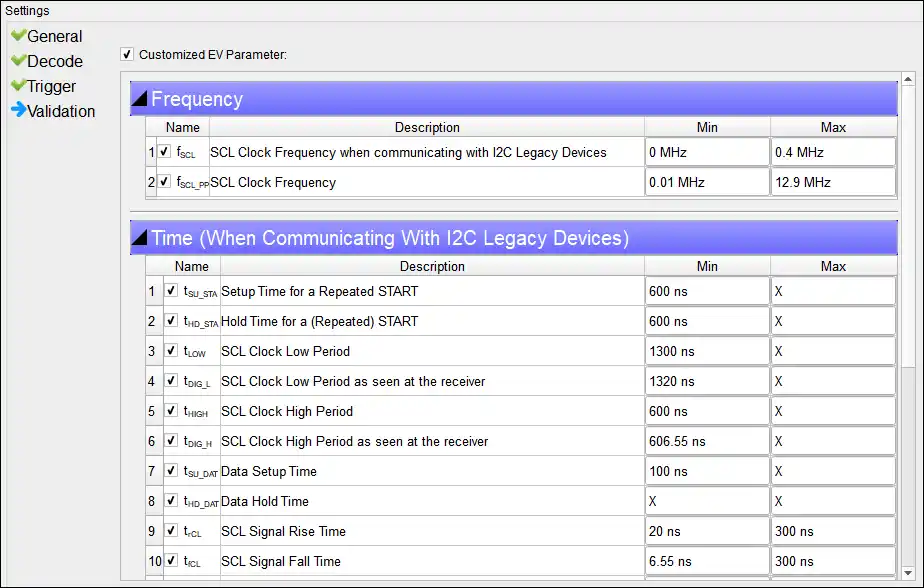

4. Validation:設定頻率、時間、電壓等驗證參數的限制範圍

本部分共包含五種參數表:

• Frequency

• I3C timing requirements when communicating with I2C Legacy Devices

• I3C Open Drain timing parameters

• I3C Push-Pull timing parameters

• I3C I/O stage characteristics voltage requirements

若為純 I3C 匯流排,則不會顯示與 I²C 裝置相關的時序表,也不會顯示 fSCL 頻率參數。

| MIPI I3C Frequency Requirements | |

| Symbol | Electrical Parameter |

| fSCL | SCL Clock Frequency when communicating with I²C Legacy Devices |

| tSCL_PP | SCL Clock Frequency |

| tBT_FREQ | HDR-BT SCL Clock Frequency |

| MIPI I3C Timing Requirements When Communicating With I2C Legacy Devices | |

| Symbol | Electrical Parameter |

| tSU_STA | Setup Time for a REPEATED START |

| tHD_STA | Hold Time for a (REPEATED) START |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSU_DAT | Data Setup Time |

| tHD_DAT | Data Hold Time |

| trCL | SCL Signal Rise Time |

| tfCL | SCL Signal Fall Time |

| trDA | SDA Signal Rise Time |

| trDA_OD | SDA Signal Rise Time (Open Drain) |

| tfDA | SDA Signal Fall Time |

| tSU_STO | Setup Time for STOP |

| tBUF | Bus Free Time Between a STOP and a START |

| tSPIKE | Pulse Width of Spikes that Spike Filter Must Suppress |

| MIPI I3C Open Drain Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW_OD | SCL Clock Low Period |

| tDIG_OD_L | SCL Clock Low Period as seen at the receiver |

| tHIGH_INIT | High Period of SCL Clock (for First Broadcast Address) |

| tHIGH_OD | SCL Clock High Period |

| tDIG_OD_H | SCL Clock High Period as seen at the receiver |

| tfDA_OD | SDA Data Fall Time |

| tSU_OD | SDA Data Setup Time During Open Drain Mode |

| tCAS | Clock After START (S) Condition |

| tCBP | Clock Before STOP (P) Condition |

| tCRHPOverlap | Active Controller to Secondary Overlap time during handoff |

| tAVAL | Bus Available Condition |

| tIDLE | Bus Idle Condition |

| tNEWCRLock | Time Interval Where New Controller Not Driving SDA Low |

| MIPI I3C Push-Pull Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSCO | Clock in to Data Out for Target |

| tCR_PP | SCL Clock Rise Time |

| tCF_PP | SCL Clock Fall Time |

| tHD_PP_Controller | SDA Signal Data Hold (Controller) |

| tHD_PP_Target | SDA Signal Data Hold (Target) |

| tSU_PP | SDA Signal Data Setup |

| tCASr | Clock After Repeated START (Sr) Condition |

| tCBSr | Clock Before Repeated START (Sr) Condition |

| tBT_HO | HDR-BT Master to Slave Hand Off Delay |

| tBT_STALL | HDR-BT Clocked Not-Ready Data-Block Headers |

| MIPI I3C I/O Stage Characteristics Voltage Requirements | |

| Symbol | Electrical Parameter |

| VIL | Low-Level Input Voltage |

| VIH | High-level Input Voltage |

| VOL | Low-level Output Voltage |

| VOH | High-level Output Voltage |

5. 電氣特性驗證軟體 控制面板:

停止條件:

當獲取資料次數達到 X 時停止

當結果錯誤超過 X 次時停止

資訊:

選擇波形

儲存檔案:

儲存為 HTML

儲存為 .MOW (Acute軟體格式)

YouTube 影片