I3C 电气特性验证 Electrical Validation

电子设计的关键之一是确保电路的正确性和稳定性。在这样的背景下,电气特性验证功能应运而生,旨在为工程师提供一个全面且便捷的平台,用于验证电子设备的各项电气特性。

皇晶科技提供的电气特性验证功能具有诸多优势,首先在于其灵活性和易用性。工程师可以轻松设置各类参数,包括电压、频率和时序等,软件则即时显示测试结果,包括波形与参考点。更重要的是,软件还可自动生成详尽的测试报告,大大节省了宝贵的时间和人力成本。

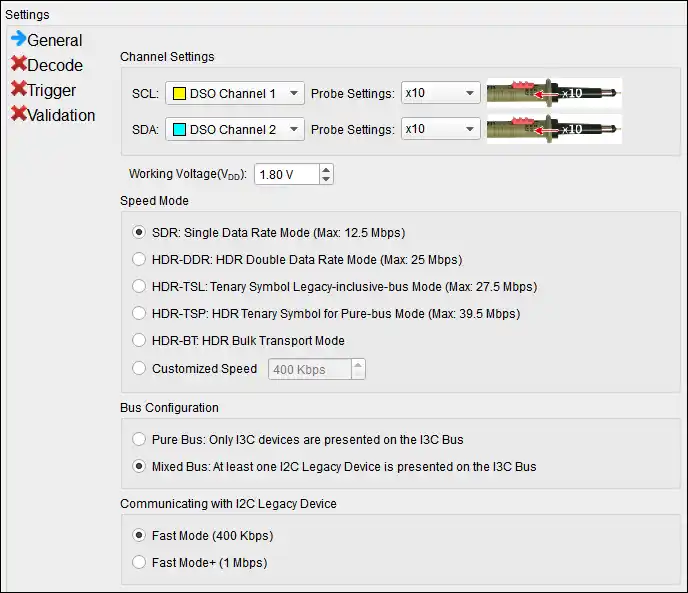

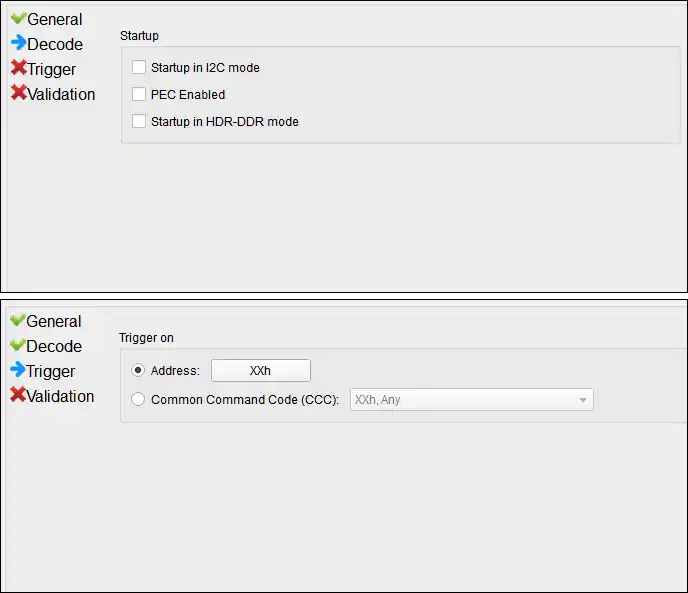

此外,在常规设置方面,用户可以指定信号来源、工作电压和速度等关键参数,以满足不同应用场景的需求。解码设置则有助于更深入地解析信号,进一步提高验证的准确性和可靠性。

该功能还支持工程师对电压、时序和频率等关键验证项目设定数值范围,软件可根据设置内容判断是否符合范围要求,从而确保电子设备在各种工况下的正确性和稳定性。这一功能的引入,为电子设计与验证工作带来了全新的效率和便利,有助于提升产品的质量与可靠性。

支持型号:

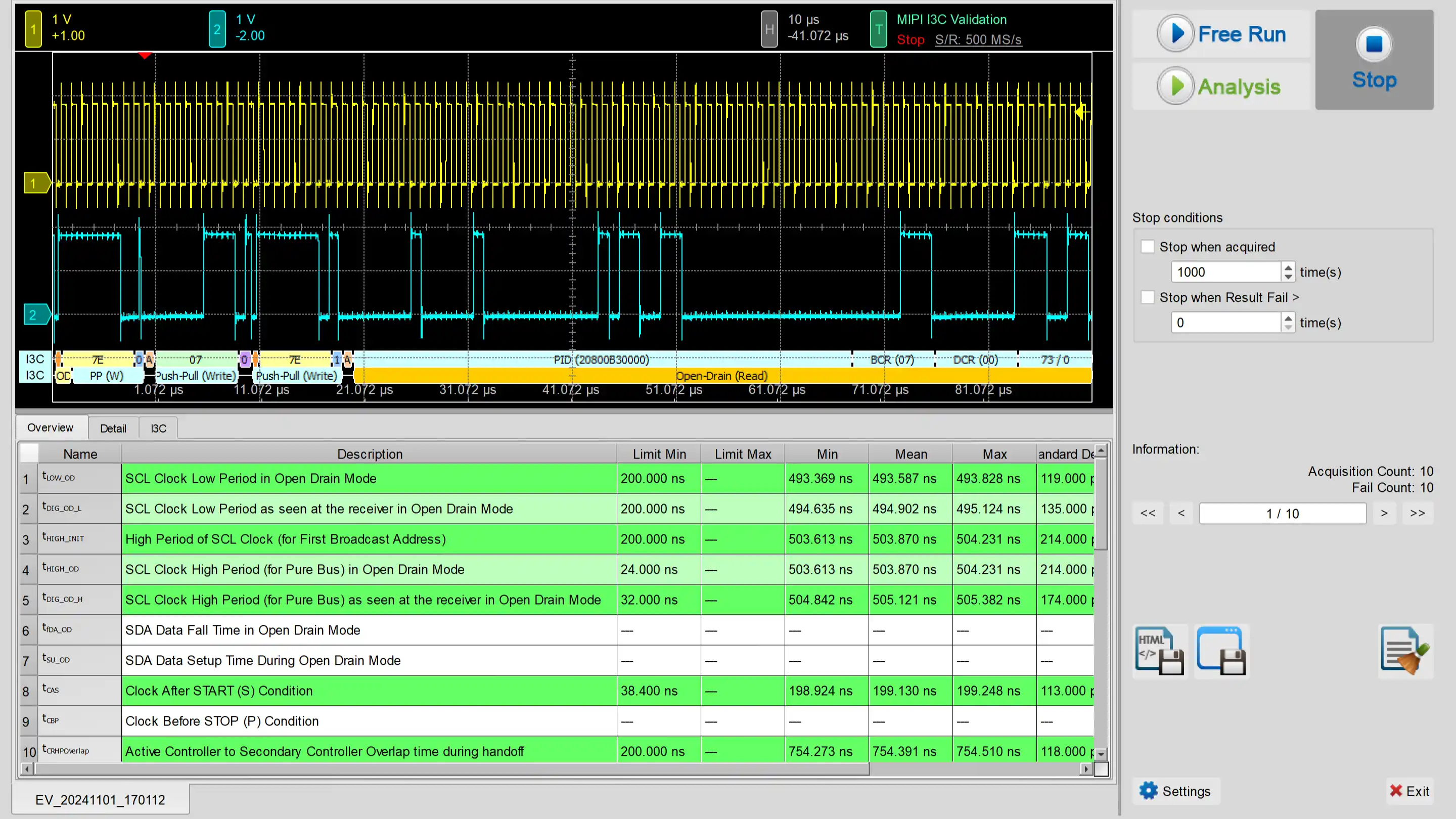

电气特性验证 软件画面

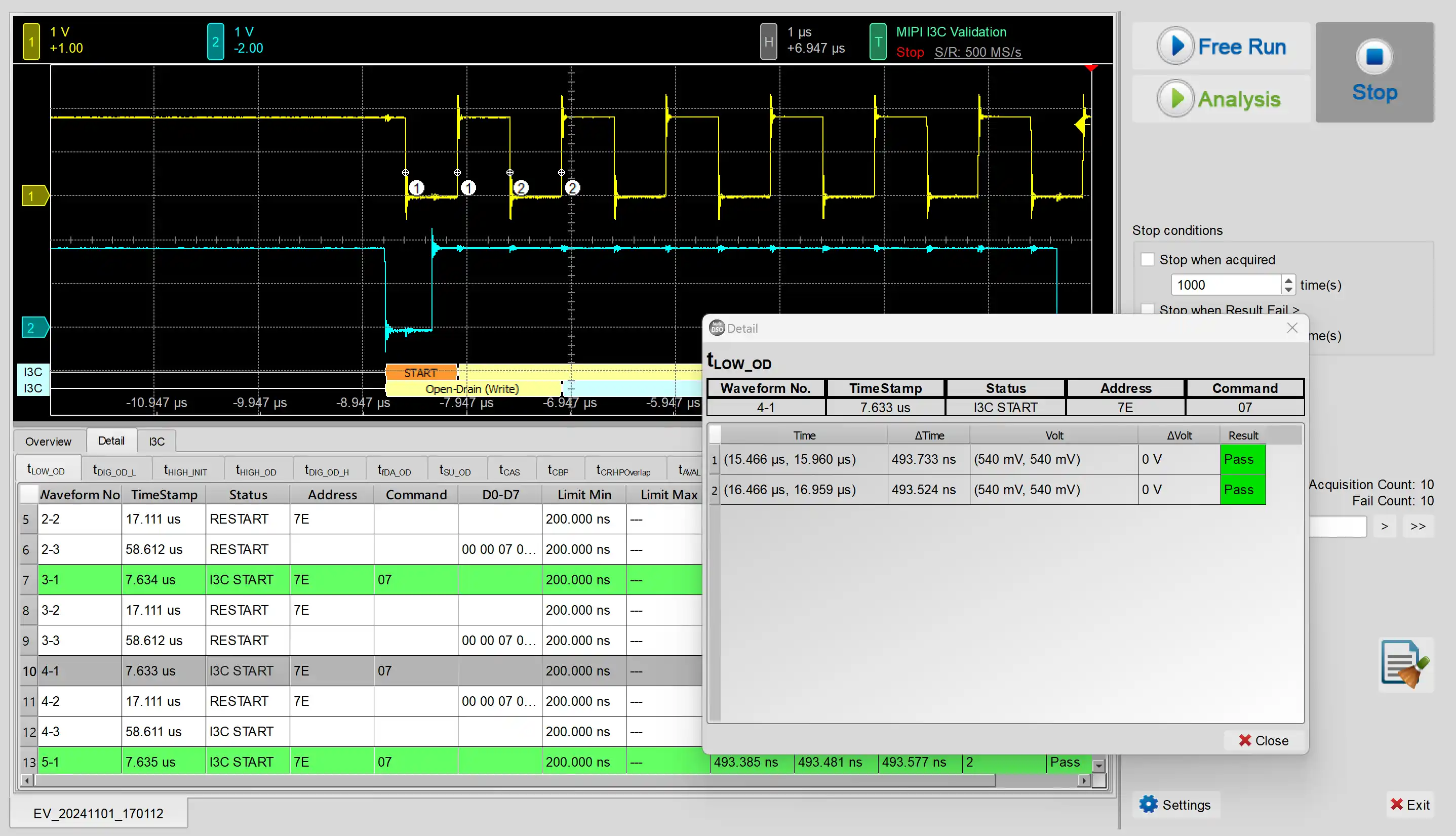

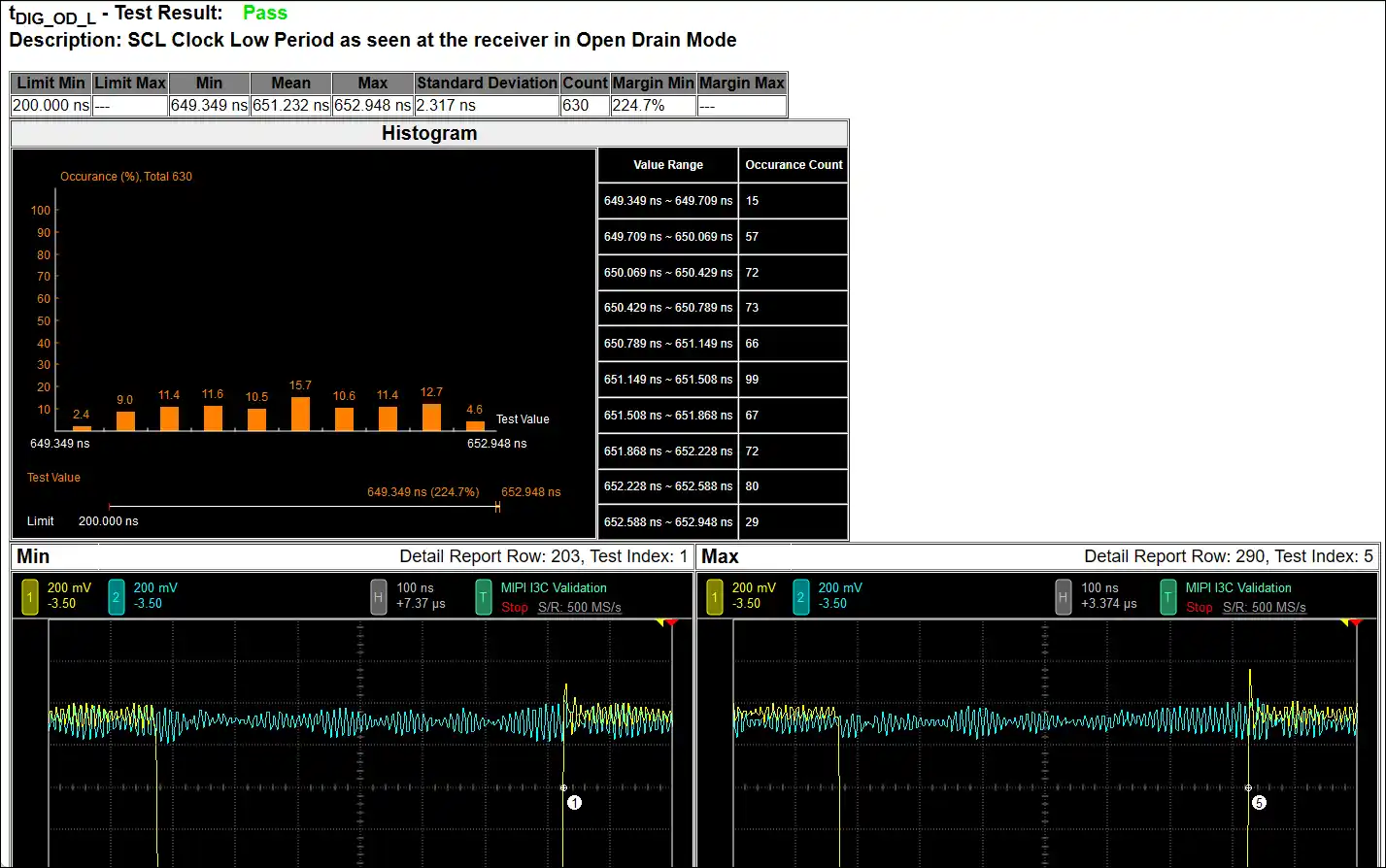

波形和参考点

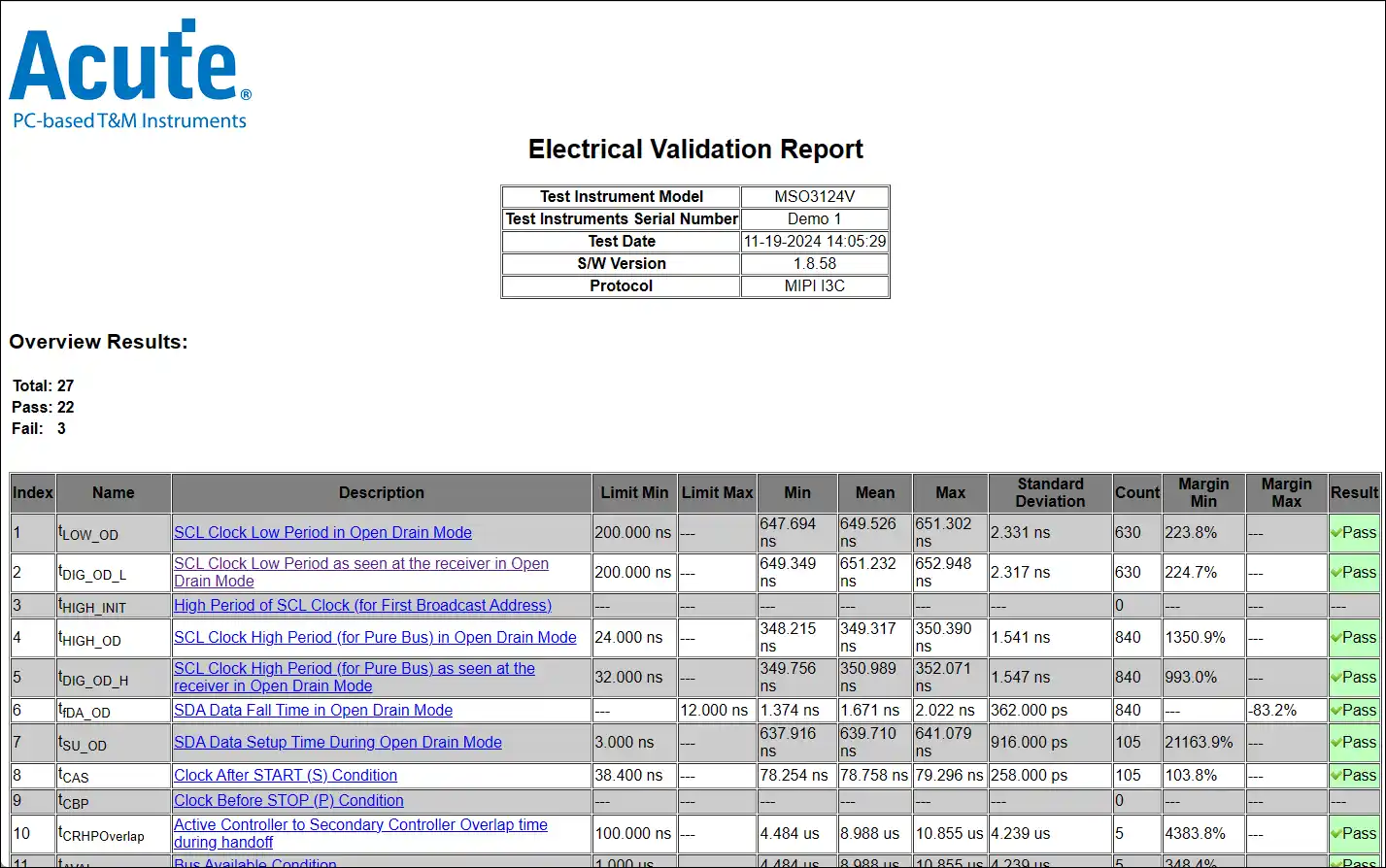

HTML 报告总表 - 有对应连结,可方便输出/查询/传递

HTML报告 详细内容

I3C 电气特性验证 设置:

1. 一般设置:通道来源、工作电压与速度

2~3. Decode / Trigger:I3C 解码 / 触发 设置

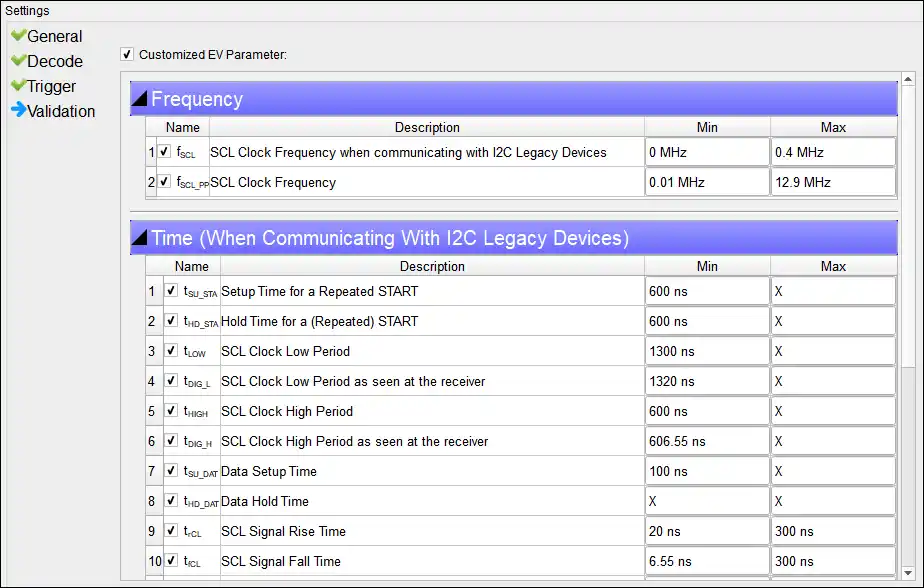

4. 验证参数设置:频率、时序与电压限制条件

本部分共包含五种参数表:

• Frequency

• I3C timing requirements when communicating with I2C Legacy Devices

• I3C Open Drain timing parameters

• I3C Push-Pull timing parameters

• I3C I/O stage characteristics voltage requirements

若为纯 I3C 总线,则不会显示与 I2C 装置相关的时序表,也不会显示 fSCL 频率参数。

| MIPI I3C Frequency Requirements | |

| Symbol | Electrical Parameter |

| fSCL | SCL Clock Frequency when communicating with I²C Legacy Devices |

| tSCL_PP | SCL Clock Frequency |

| tBT_FREQ | HDR-BT SCL Clock Frequency |

| MIPI I3C Timing Requirements When Communicating With I2C Legacy Devices | |

| Symbol | Electrical Parameter |

| tSU_STA | Setup Time for a REPEATED START |

| tHD_STA | Hold Time for a (REPEATED) START |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSU_DAT | Data Setup Time |

| tHD_DAT | Data Hold Time |

| trCL | SCL Signal Rise Time |

| tfCL | SCL Signal Fall Time |

| trDA | SDA Signal Rise Time |

| trDA_OD | SDA Signal Rise Time (Open Drain) |

| tfDA | SDA Signal Fall Time |

| tSU_STO | Setup Time for STOP |

| tBUF | Bus Free Time Between a STOP and a START |

| tSPIKE | Pulse Width of Spikes that Spike Filter Must Suppress |

| MIPI I3C Open Drain Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW_OD | SCL Clock Low Period |

| tDIG_OD_L | SCL Clock Low Period as seen at the receiver |

| tHIGH_INIT | High Period of SCL Clock (for First Broadcast Address) |

| tHIGH_OD | SCL Clock High Period |

| tDIG_OD_H | SCL Clock High Period as seen at the receiver |

| tfDA_OD | SDA Data Fall Time |

| tSU_OD | SDA Data Setup Time During Open Drain Mode |

| tCAS | Clock After START (S) Condition |

| tCBP | Clock Before STOP (P) Condition |

| tCRHPOverlap | Active Controller to Secondary Overlap time during handoff |

| tAVAL | Bus Available Condition |

| tIDLE | Bus Idle Condition |

| tNEWCRLock | Time Interval Where New Controller Not Driving SDA Low |

| MIPI I3C Push-Pull Timing Requirements | |

| Symbol | Electrical Parameter |

| tLOW | SCL Clock Low Period |

| tDIG_L | SCL Clock Low Period as seen at the receiver |

| tHIGH | SCL Clock High Period |

| tDIG_H | SCL Clock High Period as seen at the receiver |

| tSCO | Clock in to Data Out for Target |

| tCR_PP | SCL Clock Rise Time |

| tCF_PP | SCL Clock Fall Time |

| tHD_PP_Controller | SDA Signal Data Hold (Controller) |

| tHD_PP_Target | SDA Signal Data Hold (Target) |

| tSU_PP | SDA Signal Data Setup |

| tCASr | Clock After Repeated START (Sr) Condition |

| tCBSr | Clock Before Repeated START (Sr) Condition |

| tBT_HO | HDR-BT Master to Slave Hand Off Delay |

| tBT_STALL | HDR-BT Clocked Not-Ready Data-Block Headers |

| MIPI I3C I/O Stage Characteristics Voltage Requirements | |

| Symbol | Electrical Parameter |

| VIL | Low-Level Input Voltage |

| VIH | High-level Input Voltage |

| VOL | Low-level Output Voltage |

| VOH | High-level Output Voltage |

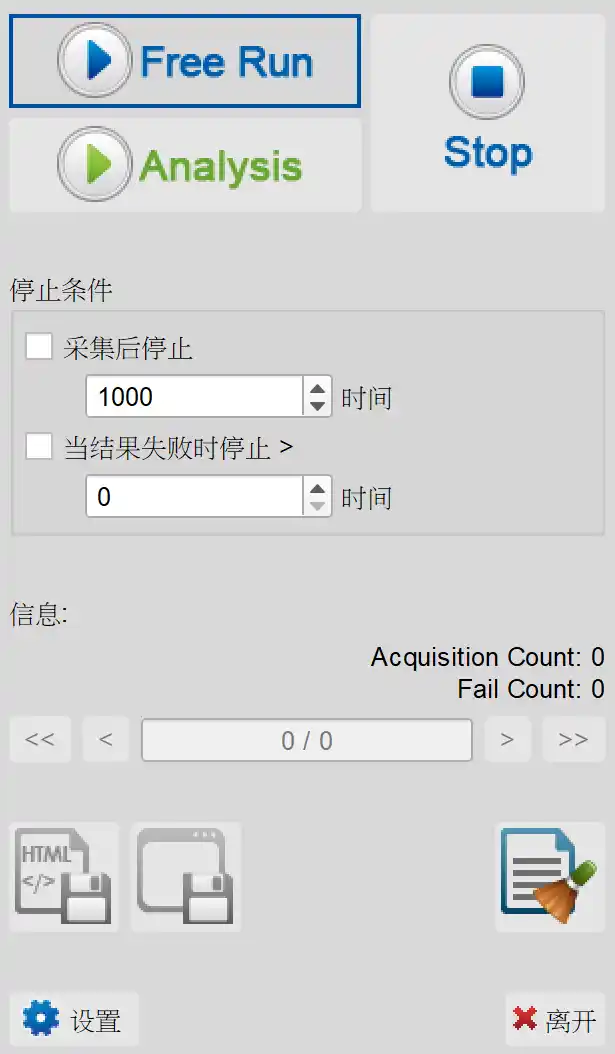

5. 控制面板

停止条件:

当采集达到 X 次时停止

当测试结果失败超过 X 次时停止

信息:

选择查看波形

储存档案:

储存为 HTML 格式

储存为 .MOW(Acute软件专用格式)